Hello there,

I bought a NINTENDO POWER Cartridge and try to program other game into it.

The original game in NINTENDO POWER Cartridge is Derby Stallion .

I programmed the Fire Emblem: Thracia 776 to the flash but the game is only black screen of death .

Did someone else have had this problem and know a way to fix this?

Does the the Fire Emblem: Thracia 776's rom has been revised for emulator ?

I usually use normal cartridges to program NP games. Did you make sure, if the game/cartridge are actually matching? HiRom/LoRom, SRAM, etc..

Ice Man wrote:

I usually use normal cartridges to program NP games. Did you make sure, if the game/cartridge are actually matching? HiRom/LoRom, SRAM, etc..

But some Games are only release in NP,like :[Genjuu Ryodan],[Super Famicom Wars]...etc.

these games has not HiRom/LoRom etc.

You're supposed to be able to tell whether a game is LoROM or HiROM from a byte in

the game's internal header.

For LoROM, byte $7FD5 will have a value of $20 or $30 and byte $7FFD will be $80-$FF.

For HiROM, byte $FFD5 will have a value of $21 or $31 and byte $FFFD will be $80-$FF.

Add $0200 to each if your image has a (redundant) floppy copier header.

nintendopower wrote:

I programmed the Fire Emblem: Thracia 776 to the flash but the game is only black screen of death .

How did you manage to write to Nintendo Power cartridges ???

I was thinking that it would be impossible to write anything to the FLASH chips without first sending some some secret unlocking commands to the MX15001 chip...

Did somebody figure out how to do that? Or is there no such protection at all? Or did you simply bypass that protection by doing some hardware mods... like desoldering the FLASH chips? Or do you have one of the official store/kiosk programming stations at home?

I just managed to pick up one of the NP SFC carts on Ebay for $20US. I'll play around with it when it arrives and let you know what I find out.

I'm almost certain he programmed the FlashROM directly. You probably don't *have* to desolder the chip to do this (

example), but it probably makes it a whole lot easier if you do.

Nintendo Power carts are not just individual games: there's a boot menu in there that also handles all the mapping for the games. If you don't copy that (and likely, modify it for the game you want to run), then the mapper doesn't set anything up and it won't work. Your best bet would be to image a real Thracia 776 NP cart and then burn that image verbatim.

I'm glad this thread exists. I've stated that I am unwilling to collect and/or dump any flash carts (BSX/NP) because they are basically USB sticks with a weird connector and raw file system. Now I have a link to show people.

If nintendopower pulls this off, he can flip $20 eBay NP carts for $400 Wizardry 1-2-3 carts until the market catches on and all NP carts lose all their value, if he were so inclined. We already have eBay sellers reprogramming NSS carts thanks to nocash's info, so this is inevitable I suppose.

I say we go ahead and do it. Reflashed NP would make a nice boot loader for my serial port controller, I keep wiping the SRAM on my current devcart and having to break out the Super UFO to rewrite it. (I guess I could dual-purpose quertymodo's Cx4 devcart though too.)

As far as reprogramming a cart through SNES code ... the actual programming of the flash chips is almost certainly the usual 0xaa55-style commands for BS-X and GBA RAM. The flash vendor interfaces are usually very similar to each other, with a few minor tweaks. But there's probably some extra catch like a "write enable" register/sequence that the NP reprogramming stations performed via running its own boot ROM instead of booting directly off the cart. Unlikely it's anything super complicated like special voltages applied to pins that a regular SNES console can't do, to turn on reprogramming mode, although I guess we can't rule that out.

Best bet to learn how to do this through cart swapping + reprogramming, would be to emulate the actual NP menu and memory mapping chip. Get a good idea of the register space involved, look for gaps in the register table, and start experimenting. Use the usual GBA RAM rewrite command style on it as you brute-force any kind of enable handshake.

But hell, it may have no enable required at all. I don't think anyone's actually tried a straight up cart swap GBA-style reprogram before.

nintendopower wrote:

Ice Man wrote:

I usually use normal cartridges to program NP games. Did you make sure, if the game/cartridge are actually matching? HiRom/LoRom, SRAM, etc..

But some Games are only release in NP,like :[Genjuu Ryodan],[Super Famicom Wars]...etc.

these games has not HiRom/LoRom etc.

EVERY SNES game has a mapper, whether it be LoRom or HiRom.

As for the cartridge itself. I used simple SHVC-1AxM-xx (LoRom) or SHVC-1JxM-xx (HiRom) donor boards from sports games and the like. Programmed the EPROMS (usually 27c801 or 27c322 with a few other decoders) and replaced the original MaskROM.

That way I have made Genjuu Ryudan, Power Lode Runner and other NP games, like the Picross series. Not for sale though!

I never had a NP Cartridge in my hands yet but I might buy one just to see how it works.

Ice Man wrote:

EVERY SNES game has a mapper, whether it be LoRom or HiRom.

This is not true. LoROM and HiROM are not "mappers". They are terms we use for two different memory models. Nintendo refers to them as "Mode ##". They are not memory mappers in the sense like NES or SA-1/SDD-1 because they aren't capable of mapping anything on the fly. They are just a static setup of how the memory is mapped.

Take Killer Instinct for example. This game consists of only two chips on a very small PCB. One 32 Megabit MaskROM and the Lockout/CIC chip. The game is "HiROM". But there is no mapper involved. The game is "HiROM" because of what signals on the MaskROM connect to what signals on the cartridge port.

My bad, "mapper" was indeed a wrong expression. HiRom/LoRom is determined whether Pin 40 is connected to A15 or not.

So why is there 7 numbers on the front? Can it hold 7 games? I didn't even know these existed until this thread! How would they program?

Yes it can hold 7 games if they are small enough to fit into the memory space given. These cartridges where programmed at stores by a Nintendo Power writer machine. Think Famicom Disk System writer, but instead it's SNES and using Flash Memory.

Interesting! Is there any write-ups on the specs for this cart? What it can and can't do? I assume it won't do any special chip games....

Does anyone here have one of the programming machines?

I picked up a few of these NP carts and they are interesting....

It appears there is a menu to select from (albeit in Japanese).

I have a DK3 and street fighter 2 hyper fighting. The cart inside has the potential of 3 16mbit flash chips but only 2 of the flash roms are installed. So it would seem that whatever can be programmed, couldn't be any bigger than 48mbits or total more than 48mbits. DKC3 is a 32mbit game so that completely occupies the 2 flash roms on the cart.

There are three chapters about Nintendo Power carts in fullsnes.htm,

http://problemkaputt.de/fullsnes.htm#sn ... rflashcard The I/O port chapter is essentially a long list of

unknown details, ie. just a list of unsolved problems.

The FLASH directory chapter is more or less complete (some details about SRAM/HiROM allocation are missing), but it's unknown if the cartridge is using that directories for ROM/SRAM allocation at all - it's also possinle that there is a

second directory stored inside of the MX15001 chip, and that the per-game memory mapping is initialized based on that info (so the FLASH directory would be merely used for GUI purposes, such like displaying the game title bitmaps).

Some things that would be interesting...

One simple thing: Dumps of more FLASH directories: That would help to figure out if there's any SRAM/HiROM allocation info in the directory.

More difficult: Somehow confirming if there is a second directory (in the MX15001 chip) or if there is none such.

Ie. doing something like desoldering the FLASH chips from one cartridge, and installing them in a different cartridge (one with differently mapped games). If that is working, then there would be apparently only one single directory (in one of the FLASH chips) (technically, that might be possible: the MX15001 chip might be able to take control of the databus during /RESET, so it might be able to read the directory info from the FLASH chip, and then map the selected game accordingly) (of course that theory won't work for bigger 4Mbyte games which come up without any menu/directory).

Being pessimistic, I would suspect that swapping the FLASH chips won't work, and that the whole (de)-soldering work would just result in crashing right after selecting a game from the menu. And even if it would work: It wouldn't really on learning how to reprogram the cartridges without soldering.

The only way to learn how to reprogram the carts is probably hacking one of the offical programming stations. As by now there seems to be little known about them. Photos of their PCBs/chipset would be nice, and one would also need dumps of their storage memory, whatever they've been using there... ROM, EPROM, FLASH, HDDs?

I'll take some pics. Maybe I'll try swapping the flash roms...if I have time.

I noticed I have 2 different versions carts..

SHVC- MMS - X1. (SF2)

SHVC -MMS - 02. Dkc3

Here's some info on programming the Nintendo Power gameboy version:

http://blog.gg8.se/wordpress/2013/02/25 ... and-tears/ - for technical info: you can skip most of the text, and look at the "appendix" at the bottom of that webpage.

Normally, writing to FLASH chips would be done by writing 8bit data to a 24bit address. If I do understand the above appendix correctly, then it seems as if one would do that same thing in a more indirect fashion on nintendo power cards: Write one 8bit data value, and three 8bit address snippets to some I/O ports (?).

Did anybody ever try writing to the Nintendo Power FLASH memory yet? If not... the first try should be, of course, directly writing to 24bit addresses. If that doesn't work, then it might worth trying the command sequences from the above appendix (the gameboy addresses at 0120h and up obviously won't work on SNES, but using address 2400h and up might do it, since the snes menu program is using that addresses, too).

If it should be possible to write to FLASH memory, then the only remaining problem would be the memory mapping, for mapping the selected game into memory.

Ok, I removed the DKC3 J flash roms from the power cart. I read them using the mx29F1610 IC type (the actual IC is mx29F1601 but I couldn't find ANY information on this IC). I compared the files I read out of the 2 flash roms to the SFC DKC j version and they compared exactly the same. SO I had this bright idea (Not so bright) to re-flash the chips to the USA version DKC3 and was going to re-mount the roms to see if it worked. BUTTTTT, when I tried to write to the flash rom, I keep getting errors... so I'm wondering if it has some protected sectors. And now my flash roms are not correct either English or the Jap version. SO I'm stuck

I've ordered some generic flash roms that *should* be the same so I'll try them when they arrive. Obviously, it'd be nice to program through the cart edges but I'm a long way from that.....

I'd really like to know how the FMGBx guy figured out those commands in the first place. Is there anyone who speaks Japanese that would be willing to try and ask him?

But this seems to make it highly likely that my presumption is correct, the GB NP carts appear to work exactly as I said the SFC NP carts should: standard commands after an I/O unlock. No special programming hardware required.

Does anyone have an SFC NP menu ROM handy? I'm curious if pressing all buttons at once gets you into a debug mode. Obviously you can't do that with real hardware (easily) or with just any emulator. You need one that allows U+D and L+R simultaneously.

That the existing games hold 32mbit of flash ROM, and yet the maximum number of games on one cart is 7 (as opposed to the more logical 8), tells me that the menu data only exists when there is more than one game. Hence if you have seven 4mbit games, you need a bit of extra room (maybe not the full 4mbit) for the menu. With just one game, they'd have to omit that to fit a 32mbit game on there.

So either the MegaChips has logic to detect the contents of the flash and set up the memory mapping on its own (for single games; Thracia 776 should be 'LoROM' and DKC3 should be 'HiROM', so it's unlikely it just defaults to one or the other) or with only simple hints from a menu ROM; or it has internal storage as well. I am thinking the former is probably more likely. Especially in light of FMGBx. The GB doesn't have address pin layout changes, but it does have MBC changes, so it'd have similar issues for multi-boot.

Markfrizb wrote:

I had this bright idea (Not so bright) to re-flash the chips to the USA version DKC3 and was going to re-mount the roms to see if it worked.

Yes, that was a bit too fast ahead : - ) Before trying to store retail ROMs on the flash chips, one should first try to swap flash chips form one NP cartridge to another. That, for games that do use

different mappings (eg. replacing a LoROM game by a HiROM game, or replacing a big LoROM game by several small LoROM games).

If that is working then we would know that all mapping info is stored in the FLASH chips, without additional important/hidden mapping info being stored in the MX15001 chip.

Markfrizb wrote:

BUTTTTT, when I tried to write to the flash rom, I keep getting errors... so I'm wondering if it has some protected sectors. And now my flash roms are not correct either English or the Jap version.

Interesting effect. Hmmm protected sectors? Does it look like so to you? Ie. do you get write errors only to certain regions, and other regions are writeable without problems?

Theoretically there should be no protected sectors: The game slots should be writeable, and the directory (at the end of the menu area) should be writeable. The menu might be write-protected, but as far as I know, it's possible to store 4Mbyte games without menu, so the menu cannot be write-protected either.

However, there might be some nonstandard commands in the flash chip, or it might use standard write-protection features (being unlocked by the programming station). Or you might simply have bad contacts on some pins - did you check if the dump from the chips was intact, eg. loading it into a emulator? If you got corrupt data on reading, then it would be no surprise if you get errors on writing.

My programmer has a pin connect function so it will tell me if a pin connection is bad. Even so, I did a comparison to the .SFC rom and it was exactly the same. So I'm certain that the chip reads were good.

Do you want me to send you the images? If the compare was the same as the .SFC, then where could the menu (and menu sound) be stored?

When I tried to write to the MX29F1601, it would error out almost immediately.... A few seconds into the program initiate. But something did change as my compare data did change in the flash chip.

I haven't tried loading the rom image into an emulator. Since it compared exactly to the .SFC dkc3j, I would bet that it would work. (I combined the 2 images into 1 4mB image to do the compare)

NoCash, I also picked up a derby98. Should I try swapping those chips to the DKC card?

And why is one card "x1" and others "02". What could be the difference?

Derby98 is LoROM, and DKC is HiROM? Then, yes, would be interesting if the LoROM game works on the PCB that has formerly contained the HiROM game.

The X1 and 02 boards seem to contain the same chipset. Some resistors/capacitors are arranged differently. It's probably just some cosmetic revision.

What do you mean by where the menu could be stored? The theory is that the menu is stored in first 512Kbytes of FLASH memory, but only if you have multiple small games on the cartridge - not if you have a single big game on it. Or did you see a menu being displayed before dumping the chips?

The programming errors might be a problem with unsupported commands, or timings, or so. If the erase command didn't work, then you would probably get the old data ANDed with the new data (ie. some bits changed from 1 to 0, but, due to the missing erase, no bits changed from 0 to 1).

I swapped the chips from derby stallion 98 to the DKC3 cart. Game works.

And it does boot to the menu first.

And I am 90% sure the DKC3 booted to a menu first but I can't swear to it.

Markfrizb wrote:

I swapped the chips from derby stallion 98 to the DKC3 cart. Game works.

That's great news! Looks as if the thing is less complex than expected (ie. no hidden data stored in the MX15001 chip).

byuu wrote:

Does anyone have an SFC NP menu ROM handy?

Here you go.

I have three games on my NP cart: Torneco no Daibouken – Fushigi no Dungeon, Super Trump Collection 2, and Shanghai III, all of which show up in the selection menu when loading this up in an emulator. So obviously, game info (and possibly, game mapping) is stored in flash ROM.

Ramsis wrote:

I have three games on my NP cart: Torneco no Daibouken – Fushigi no Dungeon, Super Trump Collection 2, and Shanghai III

Do you have details on the memory layout of the three games? Ie. are they LoROM or HiROM, and what ROM size and SRAM size (if any) do they have?

Nevermind, I've checked them myself:

File1:

http://superfamicom.org/info/torneco-no ... no-dungeon SHVC-TQ, LoROM, 12Mbit ROM (1.5Mbyte), 64Kbit SRAM (8Kbyte)

File2:

http://superfamicom.org/info/super-trump-collection-2 SHVC-AQKJ, LoROM, 4Mbit ROM (0.5Mbyte), No SRAM

File3:

http://superfamicom.org/info/shanghai-3 SHVC-AS3J, LoROM, 8Mbit ROM (1Mbyte), No SRAM

File1 has 8Kbyte SRAM as indicated by directory_entry[0005]=0040. Accordingly, the SRAM base address is raised for the following two files. Actually File2 and 3 don't use any SRAM, but their SRAM base address is raised anyways: both have [0002]=04, that confirms that [0002] contains the SRAM base address, counted in 2Kbyte units. So the format of the directory entries is now fully known:

Code:

0000h 1 Directory index (00h..07h for Entry 0..7) (or FFh=Unused Entry)

0001h 1 First 512K-FLASH block (00h..07h for block 0..7)

0002h 1 First 2K-SRAM block (00h..0Fh for block 0..15)

0003h 2 Number of 512K-FLASH blocks (mul 4) (=0004h..001Ch for 1..7 blks)

0005h 2 Number of 2K-SRAM blocks (mul 16) (=0000h..0100h for 0..16 blks)

0007h 12 Gamecode (eg. "SHVC-MENU- ", "SHVC-AGPJ- ", or "SHVC-CS - ")

0013h 44 Title in Shift-JIS format (padded with 00h's) (not used by Menu)

003Fh 384 Title Bitmap (192x12 pixels, in 30h*8 bytes, ie. 180h bytes)

01BFh 10 Date "MM/DD/YYYY"

01C9h 8 Time "HH:MM:SS"

01D1h 8 Law "LAWnnnnn" or "NINnnnnn" (eg. "LAW01712", or "NIN11001")

01D9h 7703 Unused (1E17h bytes, FFh-filled)

1FF0h 16 For File0: "MULTICASSETTE 32" / For Files 1-7: Unused (FFh-filled)

There isn't any LoROM/HiROM flag in there. Most games are LoROM. But there are at least a few HiROM games: Rockman 7, and Super Donkey Kong 3.

For Rockman 7, I have a dump of it's menu entry, and there isn't any special bit or byte in there, nothing that would indicate it being a HiROM game. So the MX15001 must apparently first map the selected game file, and then examine its cartridge header at 7Fxx and FFxx to determine if it's a LoROM or HiROM game (much like emulators are doing it, eg. by comparing the checksum value against the checksum complement - even that simple comparision would be quite amazing for a logic chip, maybe there's some microprocessor in the MX15001 for handling that task).

For Super Donkey Kong 3, markfitzb has dumped the two desoldered FLASH chips. That kind of low level dump is interesting because it allows to see how the HiROM banks are stored: In that HiROM cartridge, the cart header is located at ROM offset FFxx, which means that the ROM isn't interleaved (in that case the header would appear at 7Fxx even for HiROM games, which would simplify the mapping, but Nintendo didn't do that).

Super Donkey Kong 3 is 4Mbyte, occupying the whole FLASH memory, without menu, and without any intact looking directory entries at offset 060000h, so it seems to boot up using the cart header instead of the directory.

Oh, and mark also made a low level dump from desoldered Derby'98 chips. Derby'98 contains the menu/directory in first 512Kbytes, Super Donkey Kong 3 doesn't contain any menu/directory, so I am very sure that the latter one didn't displayed a menu.

For the FLASH chip that got corrupted by mark's write-attempt: It turned out that the whole chip is just FFh-filled. Ie. the erase worked fine, but writing didn't work for whatever reason.

If somebody has a digital scope: It would be interesting to view two signals when selecting a game in the menu:

/RESET signal, on one scope channel (used as trigger)

/OE or /CS signal for FLASH chip, on the other scope channel

Theoretically, /OE and /CS should be toggled a bunch of times

during /RESET=low (assuming that the MX15001 chip is really takng control over the databus for reading directory & cart header).

I haven't been able to find a data sheet on this chip.. The MX29F1601MC I wonder if the OE and CE are reversed maybe??? Anyone know of a datasheet? I tried to look it up on the almighty google but came up with not much useful. And the chip isn't in my programmers directory so I had to use one close to it (the MX29F1610 and similar) to read the chip.

Markfrizb wrote:

The MX29F1601MC I wonder if the OE and CE are reversed maybe???

Your overall wiring seems to be okay since you have successfully managed to send the erase command to the chip.

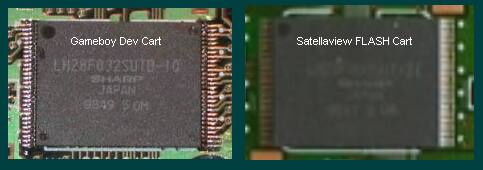

It's possible that Nintendo has bought FLASH chips with customized protocol for write commands from Macronix (for the Satellaview mini-flashcards, they seem to have bought customized FLASH chips with special ID commands).

Apropos, ID. Does your programming tool allow to read chip IDs, and if yes, what ID values does it show for the FLASH chips?

Here are some photos of the PCB front & back sides:

http://www.snescentral.com/article.php?id=0799 the picture quality is very bad. But it does look as if the thing connects to Pin 1 (master clock) and Pin 2 (expand). Master clock would make sense since the MX15001 should require some clock signal to read the separate header/directory bytes. Expand would suggest that one would need to inject some signal/voltage to that pin to unlock writing, which should be no problem, except that it couldn't be done on normal retail snes consoles.

Better photo of the PCB back side would be nice to confirm that!

EDIT: Satellaview carts have EXPAND (Cart.Pin2) wired to SYSCK (Cart.Pin57) via a 100ohm resistor. Maybe the NP carts are doing that, too?

byuu wrote:

I'm glad this thread exists. I've stated that I am unwilling to collect and/or dump any flash carts (BSX/NP) because they are basically USB sticks with a weird connector and raw file system. Now I have a link to show people.

If nintendopower pulls this off, he can flip $20 eBay NP carts for $400 Wizardry 1-2-3 carts until the market catches on and all NP carts lose all their value, if he were so inclined. We already have eBay sellers reprogramming NSS carts thanks to nocash's info, so this is inevitable I suppose.

I say we go ahead and do it. Reflashed NP would make a nice boot loader for my serial port controller, I keep wiping the SRAM on my current devcart and having to break out the Super UFO to rewrite it. (I guess I could dual-purpose quertymodo's Cx4 devcart though too.)

.

Does Wizardry123 only work on the NP cart? I got it to load on a Lo Rom cart but can't start the game. gives my a system file message error "wiz1 sys file" and then a bunch of Japanese characters..

Thanks

Markfrizb wrote:

a bunch of Japanese characters..

ファイルが、こわれています。

"The file is broken/has failed."

Wierd. It boots with animation and sounds.... Just won't go into a game.

I did use the English translation so I need to try the original next...

Edit: tried original J version. Same result.

OK, I got my MX29F1610MC flash roms in today. I programmed the DK3 that came on the cart to begin with. As a reminder, the original roms are MX29F1601MC. They both got hot real fast! needless to say the game didn't work. So what would make the cart get real hot?? the heat was from the roms. SO if I can read the roms just fine, why wouldn't the cart read them also? REALLY need a datasheet for the MX29F1601....

Oh, and I've mounted these before without issue so I don't believe the problem was mounting.

Markfrizb wrote:

Wierd. It boots with animation and sounds.... Just won't go into a game.

Maybe it's actually talking about the save data? (assuming it saves progress, I have no idea about that game) What happens if you wipe it?

Sik wrote:

Markfrizb wrote:

Wierd. It boots with animation and sounds.... Just won't go into a game.

Maybe it's actually talking about the save data? (assuming it saves progress, I have no idea about that game) What happens if you wipe it?

I've tried everything possible. Tried to change, delete, alter, rename..... nothing will get this to go into game mode.

I burned the original Jap version, and it acts the same way.

edit: I using a 1A3M host cart. I even tried it on a 256k cart. no difference

Markfrizb wrote:

So what would make the cart get real hot?? the heat was from the roms.

How in the hell would we know that? :P

It's not because Wizardry 1-2-3 is stored on them, I can surely tell you that much.

I've only ever had chips boil when I ended up crossing wires or connecting them wrong.

ICs in general more or less only ever get hot because of bus conflicts, using the wrong voltage supply, or being given invalid voltage inputs causing both FETs on an input stage to be on.

lidnariq wrote:

ICs in general more or less only ever get hot because of bus conflicts, using the wrong voltage supply, or being given invalid voltage inputs causing both FETs on an input stage to be on.

I was hoping for someone would use their crystal ball. I figured there are significant differences between the flash roms....

I was hoping for suggestions on where to start looking. I know it wasn't because of game program on them (DK3 was programmed by the way, not Wizardry).

If my programmer can read the chips (read them as if they were the MX29F1610MC) then I would think that the data and address lines are the same. And probably the /CE and /OE as well..... whats left beside /WE...

I'd test Vcc first, because it's by far easiest (and fast). After that, Vio seems more likely but more involved.

Markfrizb wrote:

OK, I got my MX29F1610MC flash roms in today. I programmed the DK3 that came on the cart to begin with. As a reminder, the original roms are MX29F1601MC. They both got hot real fast! needless to say the game didn't work. So what would make the cart get real hot?? the heat was from the roms. SO if I can read the roms just fine, why wouldn't the cart read them also? REALLY need a datasheet for the MX29F1601....

Oh, and I've mounted these before without issue so I don't believe the problem was mounting.

Hard to say, but just throwing random ideas out there, the MX29F1610 comes in a "reverse type" where the leads are bent backwards in order to simplify placement on opposite sides of a board, might want to check that you don't have one of those, or you'd have it soldered in backwards. I can't find a datasheet for the original chips, but

here's the datasheet for the 1610. That being said, my money would still be on a soldering issue, like an improperly seated chip or soldering short.

Cool. Interesting to see the MX-chip pinouts. Some comments...

Marking not-installed resistors would be nice (eg. as "N/A" instead of just leaving the description blank).

Some more wires (and bold address/data bus lines) might also help to see what goes where.

I would have probably numbered the FLASH and SRAM A0,A1,A2... address lines the same way as on SNES side (instead of using the shifted 16bit FLASH chip numbering.

The "MC" signals, MC35 and MC36 are connected to the battery controller... and the other MC's like MC38, MC_72, MC_74, MC_96... are they connected anywhere? I can't see there, although there is a short green wire attached to those pins (which is somehow suggesting that they are connected, if they aren't then I would leave them without green wire, and without external signal name (ie. only use an internal pin)).

Going by a PCB photo, there seems to be a via between R11 and R12, so there's probably something more connected there (just two resistors in series wouldn't make too much sense anyways, especially if one of them isn't installed).

Oh, nice to see SYSCK being passed to EXPAND via R14. It's same as for Satellaview carts (ie. apparently intended for passing SYSCK to the satellaview receiver unit on expansion port). Btw. you forgot the resistor value for R14 (going by PCB photos it's having 100 ohms installed, which would be also same as in satellaview cartridges).

R1 and R4 are 510K and 510 ohm accordingly (not 500K and 500). If you can decipher the part numbers on the real board: There are hires PCB photos earlier in this thread (the 3-digit numbers are reading as NN and number-of-zeroes, eg. 123 = 12000 ohm = 12K ohm).

There seem to be further vias near R1 and R4 which aren't showing up in the schematic. And more vias on A12 and A23 on the cart edge connector. There seems to be stuff missing in the schematic, unless the vias are dead-ends without connection (btw. a photo of the PCB bottom side would be nice).

On PCB front side, cart edge pin 32,33,34,35, and 49, and 60,61,62 are not connected (probably more on bottom side). Would be neat to indicate that in the schematic. I guess your CAD software autogenerated wires on each pin - but it should (hopefully) allow you delete that wires in cases where the pins aren't connected.

Thanks for your input, really appreciate it.

You're absolutly right about R11 and R12, R11 goes to the MegaChips' Pin 38.

MegaChips 96 is connected to the edge connectors reset pin.

Still can't find MegaChips pin 72 and 73.

Thanks for the update and PCB photos!

MM1134 pins should be as so:

Code:

.-------------..-------------.

1 | GND VCC | 8

2 | /RESET (out) /CS (in) | 7

3 | CS (out) Vout | 6

4 | Vbat (in) /CS (out) | 5

'----------------------------'

So MC36 would be /SRAM_CS (forwarded from pin7 to pin5 when VCC is good).

And MC35 would be /RESET (low when VCC is bad), that would serve as power-on reset signal for the MX1500. The other /RESET pins (MX1500 pin 96 and 100), one of them should OUTPUT to SNES (when starting a game selected in the bootmenu), and the other one is probably INPUT from SNES (on power-up, or when pushing RESET button). No idea which is input and which output since they are just shortcur together.

MX1500 pin 30 + 31 are apparently oscillator inputs (could be named OSC1 and OSC2 or so), in this case driven by the 21MHz master clock SNES rather than using a separate oscillator.

MX1500 pin 29 and 38 are still looking weird. If there's no other connection to those pins then I've no idea what they could be good for. My first idea would have been pin38 = /SRAM_WE, but it seems that the SRAM write enable is shared with /FLASH_WE3.

MX1500 pin 72 and 73 could be anything. Are they wired to any vias (underneath of the chip) or are they just not connected? One guess would be that they could be upper address lines for FLASH memory (Nintendo is often doing that: outputting the higher address bits together with separate /CS1 and /CS2 signals), maybe intended for testing/debugging, or allowing to use a single big FLASH chip instead of 2-3 smaller FLASH chips in future hardware revisions... though in that case they would also need an option for merging the /CS1,2,3 and /WE1,2,3 signals to single pins.

MX1500 pin97 might be some mode selection input, that could be pulled high or low by installing either R9 or R10. Maybe for selecting between multiple small FLASH chips and single large FLASH chip. Or for indicating if the 3rd FLASH chip is installed. Or whatever. Some of the GNDed pins might be also whatever mode selections.

Oh, and C5 should connect to pin91 instead of to R9 (they are both VCC, so it would matter only for context & signal run time).

EDIT: CIC_10 could be called /CIC_RESET or /CIC_ERROR. It should get low (pulsed) on CIC region errors. And it might also get low on power-up or when pressing Reset button (in that manner it would be a 4th reset signal on the MX1500 chip, doubt that the MX1500 relies on this extra reset input). When using the cartridge with non-japanese consoles, then one would probably cut the CIC_10 signal, and strap MX1500 pin 93 to VCC (?)

Turns out MX1500 pin 29 is VCC

Ah, then everything makes more sense (and pin 38 would be another "mode select" input with either R11 or R12 installed, similar to pin 97).

Could you check R7 and R8, too? Both would make more sense if they would go to VCC instead of GND.

PS. and double check if FLASH_WE3 is really shared as SRAM_WE? It's possible, but looks quite odd. But having three separate FLASH_WE signals is odd anyways, no idea what they have intended there.

PPS. why is the schematic called "Nintendo SF-Memory Cartridge"?

"Nintendo Power Cartridge" would appear more obvious to me : -)

WE is shared between the 3rd Flash and the SRAM, just double checked again to be sure.

Okay, you are right. Thanks for checking!

One small detail: the signal on MX1500 pin 34 should be marked GND.

So I desoldered the two MX29F1601 flashroms out of my NP cart and wrote a programmer based on Arduino for them. It works but takes 4 hours because I am supposed to write 128 bytes at once but I only write one byte at a time. Because otherwise I get alot of unwritten bytes. So no special write commands, no protected sectors, just a changed protocol that I don't fully understand, which is why it takes 4hrs to write them.

Now I did the following tests:

- flashed a retail Illusion of Gaia to one of the MX29F1601 and put the flashrom into a standard hirom pcb to confirm that you can indeed flash the MX29F1601 -> it worked flawlessly

- flashed a retail Illusion of Gaia to one of the MX29F1601 and put the flashrom back into the Nintendo Power cartridge -> didn't boot

- downloaded Wizardry 1-2-3(from some emu site), split it into two and flashed it to both MX29F1601 -> didn't work

- flashed back the Derby Stallion 98 with menu that was on there before -> worked

My conclusion, that could be wrong, is that when the rom you flash has a menu you can flash the MX29F1601's and it will work. If you flash something that doesn't have a menu it won't boot. Most likely there is something in the MX1500 chip that needs to be setup if there is no menu.

I did not have any luck flashing the MX29F1601 while they are still soldered into the NP cart even though I connected the missing WE/OE pins to the Arduino flasher. The data lines are connected straight through to the cart connector as you can see in the schematic I posted earlier but the address lines are not and not everything you send to the cart edge connector will come out of the other end of the MX1500 chip. At first it did but then the MX1500 chip somehow locked up idk. I have no clue what I am doing tbh.

Interesting and good to know that write commands are working, at least with 1-byte writes.

Aside from being slow, issuing 128 separate writes per sector will also reduce the chip's lifetime by factor 128.

Did you test your code with both MX29F1610 and MX29F1601 chips? Ie. are you sure that the "can write only 1 byte" problem occurs only for the Nintendo Power chips, or could be a general problem with your code?

For the "delay(7)": Erasing/writing flash memory does take some time, so you would need some similar delay also for normal 128-byte writes. Usually, the chip should output some "busy/ready" info, so you would wait for that info instead of using a hardcoded "delay(n)". Going by the MX29F1610 datasheet, data.bit7 should indicate ready. Or are you doing that kind of wait somewhere outside of the write function?

Datasheet also says that gaps between multiple byte writes may not exceed 30us. That might also cause lost writes in case the arduino is too slow, or in case it gets interrupted by IRQs.

NB. what is delay(7), seven microseconds, or seven milliseconds?

I started with the 29F032 flashrom and wrote an Arduino Mega based programmer for that, then continued to the 29F1610 and 29L3211 and finally tried to apply what I learned to the NP's 29F1601.

I'm a beginner when it comes to programming, hence working with Arduino.

Yes the delay is also needed with the 29F1610, but since I can write 128bytes per delay it's not that bad. The delay is in milliseconds (1/1000s), so it's quite long if you have to delay after every written byte.

Reading the status register while the flashrom is programming itself would be much much better, I tried that but couldn't get it to work so I kept the delay.

The next step would be to be able to program the flashrom inside the NP cart without the very tedious process of desoldering the flashroms.

I got an own nintendo power cart, too (thanks to skaman). And started some hardware tests today. Some first findings:

The thing initially didn't want to boot, but worked after a few attempts with inserting/removing the cartridge, maybe the contacts in my console were just a bit dirty. I am a bit surprised that it is working in my PAL console (with the PAL-CIC disabled in the console). I would have expected needing to disable the NTSC-CIC in the cartridge since it's passing some "ERROR" signal to the MX15001 chip... but apparently that signal doesn't protect the NTSC cart agaist being used in (modded) PAL consoles. Well, just fine.

Next surprise is that the boot menu music is quite moderate. After having listened the Satellaview and DSi bootmenu music themes, I was having the impression that Nintendo planned to create an army of labile teenagers running amok and to randomly shoot other people just because they are scared and distracted about the world that they are living in. But, for the Nintendo Power menu, the music is quite okay (just gets a bit boring when listening to it for about 30 minutes). Hmmm, maybe I was wrong and Nintendo never really intended to provoke amok and they are just tend to have a real/unreal bad taste in music. Anyways.

The Reset button is handled other as I would have expected: Within the menu, it does just restart the menu. But after selecting a game, it does restart the selected game. Only way to return to the menu seems to be switching power off/on? Can somebody confirm that? (just in case it happens only on my modded PAL console).

Reading the I/O area returns value 7Dh for addresses 00h:2400h..2407h (no matter if menu or game is being selected). Addresses 00h:2408h and up are open bus. And there are no mirrors in other banks (tested banks 01h, 10h, 20h, 80h, and they are all open bus).

Next, I've also had a look at the menu of the nintendo power gameboy version. One difference is that it's having some simple selftest mode, which is making a bit easier to get an idea what kind of commands are being used/supported. The used port [0120h] command numbers are 09h, 04h, 05h, 08h for whatever purpose, and 8xh and/or Cxh for game(x) selection. All commands seem to be terminated by [013Fh]=A5h. Command 09h should be prefixed by a dummy read from [0120h], and seems to require two fixed parameters: [0121h]=AAh, [0122h]=55h. The other commands don't use any parameters at all. The "decode data" selftest displays a 24bit value read from [0122h..0124h], and does then verify if [0122h..0124h] is A8h,00h,00h. The "menu sequence" selftest checks if [013Fh] is A5h.

The homebrew source code snippets for programming nintendo power gameboy carts are using command 09h and 04h, too. Plus commands 01h, 02h, 0Ah (also without parameters), plus command 0Fh (with 8bit data and some incomplete looking 16bit address). I am still wondering who has reverse-engineered those extra commands and how. Either somebody did have access to an official programming station - or somebody just randomly tried sending commands & parameters to see if any of them would pulse pins on the FLASH chip. Considering that most commands don't require any secret parameter values, that method should be actually working - without even needing any other equipment than a LED or volt-meter.

Going by the part number, the SNES chip seems to be a bit older than the gameboy chip. And it doesn't seem to require any equivalent to the gameboy's trailing [013Fh]=A5h write. So, the SNES chip might be even less complicated than the gameboy chip. At the moment, I am optimistic that it'll be cracked in next 24 hours...

"Within the menu, it does just restart the menu. But after selecting a game, it does restart the selected game. Only way to return to the menu seems to be switching power off/on?"

It does exactly the same on my Super Famicom. Also when in the menu you can hold X and it shows you where the game is stored and how much space it occupies by flashing the F and B symbols.

As for the GB NP cart it seems like the commands where found by doing some educated guesswork and using a lot of probes:

"Combination of numbers will become the astronomical number, but look at the behavior we will squeeze to guess the command format."(Translated by google from this source

http://mootan.hg.to/fmgbx/)

Yeah, I've seen that photo. It's a bit hard to make sense of it. The stupid theory would be that the software for the blue cartreader did have nintendo power support included, and that the guy reverse engineered the software with a logic analyzer instead of disassembling the cart reader software directly. But that would be just stupid.

Other theory would be that the cartreader was just used for doing the tests on a PC instead of on a real gameboy. The connection is weird though. The nintendo power cart-edge seems to be on the left (=without direct connection to the cartreader on the right). Maybe there's an adaptor from left-to-right underneath of the cartridge, and with additional wires on the left for forwarding the cart-edge signals to the logic analyzer (not that one would need to analyze the cart edge signals that one is sending to the cart, since one should know what one is sending anyways; but it might be helpful to log the sent-commands alongsides with the cart-internal signals). Inside of the cartridge, most wires seem to go to the SRAM chip (makes sense since it has the biggest solder pads).

As far as I understand it, the NP cart plugs into some cheat device like a Blaze xploder or Action Replay

and through that it plugs into the blue Bung flash linker.

The cheat device is probably just used so he has better access to the NP cart since that way it's not hidden away inside the blue Bung flasher's cart slot.

Then he send commands from his pc through the Bung flasher to the cart edge and read the results if any on the sram chip inside the NP cart.

My guess is that they hooked it up to that device just as a PC interface to send arbitrary commands to the cart, then they have the probes set up to log the output result of the commands. Chances are, the SNES cart has an unlock sequence similar to the GB one, and you could try to bruteforce it by sending a single byte sequence to each address, and cycle through every address/data combination, then try a two-byte sequence, then three, and basically monitor the ROM /WE line. If you manage to get the /WE line to go low, then you've found the unlock sequence. However, as the poorly translated page says, the number of possibilities quickly becomes incredibly large. You could start with some commonly-used values to start though, such as 0x55, 0xA0, 0xAA, etc. as data values.

Oh, yes, the yellow Blaze thing looks like the gray case on the other photo.

Writing commands to the FLASH chip seems to be no issue, writing the chip ID commands works without problems, it does even seem to work without needing to send any of the special nintendo power commands (like those being sent in the menu). I've tried this:

Code:

mov a,0aah // mov [far 018000h + 1555h*2],a

mov a,055h // mov [far 008000h + 2AAAh*2],a

mov a,090h // mov [far 018000h + 1555h*2],a

mov a,[far 008000h] ;returns C2h, maker (Macronix)

mov a,[far 008001h] ;returns zero (unused, aka MSB of maker)

mov a,[far 008002h] ;returns F3h, device (MX29F1601MC)

mov a,[far 008003h] ;returns zero (unused, aka MSB of device)

mov a,[far 008004h] ;returns C2h (probably "sector protect" flag, not maker)

mov a,[far 008005h] ;returns zero

mov a,[far 008006h] ;returns zero

mov a,[far 008007h] ;returns zero

Unlike as in the gameboy source snippets, the writes are done directly to cartridge memory space (rather than writing HH and LL and DD bytes to the MX15000x registers; though the SNES

might support that indirect write method, too).

The MX29F16xx chips are having 16bit databus, hence the "word addresses" in the datasheet are meant to be multiplied by 2 for "byte addressing" (ie. word address 5555h would be AAAAh in byte addressing, with the SNES LOROM mapping, that'd be 01:AAAA, ie. the above "mov [far 018000h + 1555h*2]" opcode).

For programming the FLASH memory, the main issue would be probably finding a way to unlock the /WP pin (ideally by software, although doing it by soldering would be "easier").

The other issue would be getting access to the whole FLASH memory (writing to the LOROM space of a cartridge with MENU does probably allow to access only the mapped 512Kbytes) (a possible workaround might be overwriting the MENU's cart header by a "bigger" cart header, reset the cart, and hope that the MX150001 chip will see the new header and map the whole memory, so one could then write a bigger file, or rewrite the menu with multiple smaller files).

I've also tried issuing the commands from the menu software:

Code:

mov a,09h // mov [002400h],a ;\NP_CMD_09h

mov a,[002400h] ;dummy ;

mov a,28h // mov [002401h],a ;

mov a,84h // mov [002401h],a ;/

mov a,06h // mov [002400h],a ;\NP_CMD_06h

mov a,39h // mov [002400h],a ;/

Don't know what CMD_09h is good for, maybe it's just needed as prefix for unlocking other CMD's (looks a bit like so in the gameboy menu).

CMD_06h seems to toggle port 2400h..2407h to return either eight 7Dh bytes, or bytes 2Ah,00h,2Ah,2Ah,03h,AAh,AAh,00h (it can be sent multiple times to toggle between the two responses). Whatever that's intended for.

Ah, and here's a summary of the different IDs (from datasheet's and from actual cartridge):

Code:

Manufacturer ID:

C2h = Macronix

Device ID:

FAh = MX29F1610A ;\with sector_protect, suspend/resume, without sleep/abort

FBh = MX29F1610B ;/

F7h = MX29F1611 ;-with sector_protect, suspend/resume, sleep/abort

6Bh = MX29F1615 ;-without sector_protect, suspend/resume, sleep/abort

F3h = MX29F1601MC ;<-- undocumented, used in SNES nintendo power carts

Tried the gameboy unlock stuff (commands 0Ah,04h,01h,02h). The SNES doesn't seem to require commands 0A,04,01h. The /WP pin is getting HIGH when just sending SECRET command 02h (preceeded by the OFFICIAL normal SNES bootmenu commands). Ie. this sequence:

Code:

mov a,09h // mov [002400h],a ;\

mov a,[002400h] ; NP_CMD_09h

mov a,28h // mov [002401h],a ;

mov a,84h // mov [002401h],a ;/

mov a,06h // mov [002400h],a ;\NP_CMD_06h (send this only if above read has returned 7Dh) (not if it's already returning 2Ah)

mov a,39h // mov [002400h],a ;/

mov a,02h // mov [002400h],a ;-NP_CMD_02h causes 2A,04,2A,2A instead of 2A,00,2A,2A --- and does set /WP=HIGH

Whoa, one must write 02h to 002400h. That's just... incredible ;- )

Testing some other random commands did also have some effects (mostly changing some of the 2A,00,2A,2A,03,AA,AA,00 response values):

Code:

;mov a,04h // mov [002400h],a ;-NP_CMD_04h causes FE,61,A5,00 instead of 03,AA,AA,00

;mov a,0ah // mov [002400h],a ;-NP_CMD_0Ah no effect

;mov a,01h // mov [002400h],a ;-NP_CMD_01h causes always 8x7D

;mov a,02h // mov [002400h],a ;-NP_CMD_02h causes 2A,04,2A,2A instead of 2A,00,2A,2A --- and does set /WP=HIGH

;mov a,00h // mov [002400h],a ;-NP_CMD_00h hangs?

;mov a,03h // mov [002400h],a ;-NP_CMD_03h causes 2A,E0,2A,2A,FF,FF,FF,FF and /WP=LOW

Tried sending the FLASH write command. Doing it as described in datasheet (or as in sanni's 29F1610 source) doesn't work out for the 29F1601 chip. It's causing odd effects: Outputting weird status values on databus, even after trying to issue the "Read/Reset" command, so one is receiving those odd status values even on following "Read ID" commands.

So, I checked sanni's 29F1601 source code again... and, yes, writing the data byte twice is doing the trick: The chip is then outputting correct status values, and returns to normal state when issuing "Read/Reset".

Trying to write a different value didn't work as expected, the result got ANDed with the old value (I was thinking that the chip would automatically erase/rewrite the written page, which should works as so on modern FLASH chips, but the 29F1601 can apparently only change bits from 1 to 0).

Next, tried to write multiple bytes: Writing each byte twice didn't work, it caused only the first byte to be written. So write-twice is apparently terminating the write command. Writing all bytes (except last byte) once, and then writing the last byte twice seems to work okay. Then wait for status.bit7 to become set (in case of the arduino code, don't forget to switch to read-direction for status reads (read address can be probably anywhere, as long it's on the

same FLASH chip; I used reading the address of first-written byte, or the last written-address should be fine, too), and remove all that delay(20) and delay(7) stuff).

---

Todo would be trying to find out how to access the whole FLASH memory. Or, well, maybe it's already fully accessible (I haven't yet tested if the the chip is booting up with/without memory being restricted to the 512Kbyte menu area).

And one thing that would be great is logging the traffic on the databus after switching from the menu to a game. That's something that can't be done on a SNES console (at least not without external extra hardware). But your arduino cart-readers should be quite optimal for doing that tests, somehow like so:

Code:

- output the game-select command (as done by the menu)

- set data direction to input

- manually issue LOW and HIGH pulses to the "21MHz" pin

(ie. wrire some output to that pin, then switch it LOW and HIGH by software, with some "nop" delays)

- after each clock pulse, read the databus, and output its value to PC (via COM port or SD card or whatever you have)

That would be great for seeing if/what values the chip is reading from FLASH memory.

Logging the state of the cart-edge /RESET pin alongsides with the databus values would be neat, too.

The "21MHz" is probably internally divided, so you'd probably see each value on several clock pulses.

The chip is probably doing that on initial power up, too (so you may need to issue LOW/HIGH pulses to "21MHz" pin after power-up, too).

Can the data bus be observed non-invasively by hooking a logic analyzer up to the

clock port on the bottom of the Super NES? Or is the clock port driven only when the B address bus is also driven?

Amiga clock port like this:

http://www.ianstedman.co.uk/Amiga/amiga ... _port.html ? I don't see too much relation between the 80pin/22pin Amiga Clock Ports and the 28pin EXT port on SNES.

For hooking the EXT port, nobody is having a connector for it, so one could only connect wires to the EXT port solder pads (which are quite well accessible, so the EXT port may be actually good for such stuff). It doesn't have a good clock signal (ideally the 21MHz master clock), so that would need to be picked up elsewhere (to get an idea when new data values are being output).

Anyways, sanni and skaman are already having fully working hardware attached to the nintendo power cartridge (except still needing to output the "21MHz" in slow-motion on one pin). So they would essentially need to switch the data direction to "input", and then just READ what is happening on the databus on each clock cycle. That should be the simpliest solution, and the data could be logged as desired (plain ASCII HEX values, or plain binary file) (logic analyzers could probably do that, too, but usually they are producing bitmap graphics with waveforms instead of raw data).

What I would have in mind, could look as so (showing input from /RESET pin as one digit, and input from DATA as two digits):

1 FF

0 03

0 07

0 A3

0 80

0 5C

0 7F

1 FF

1 FF

1 FF

Then one could see which values are read during /RESET=0, and search those values in the ROM-image, and probably guess the addresses where they are read from (=presumably from the menu's directory entry for overall mapping, and from the game's cart header for lorom/hirom detection).

Never could get the Nintendo Power or even any SA-1 game to work on my Arduino cart reader, skaman got them to work though, must be some hardware issue on my side. So we'll have to wait for him.

That doesn't mean much without the /OE and /WE signals. For all we know, that's just the ROM data being read by the console.

nocash wrote:

Trying to write a different value didn't work as expected, the result got ANDed with the old value (I was thinking that the chip would automatically erase/rewrite the written page, which should works as so on modern FLASH chips, but the 29F1601 can apparently only change bits from 1 to 0).

This is an expected behavior for any Flash/EPROM. Erasing sets all of the bits to 1, and programming can only set them to 0. In order to set a bit to a 1, you have to erase it, then reprogram the new value. So, by writing two different bytes to the same address, since you can't set any of the bits back to 1, you end up writing all of the 0's from each byte, aka ANDing them together.

Tried some more "commands":

Code:

;mov a,00h // mov [002400h],a ;-NP_CMD_00h RESET and map GAME14 ? (issues /RESET pulse) (and ONCE: did held /RESET=LOW forever) (somehow IGNORED when followed by further 240xh writes?)

;mov a,01h // mov [002400h],a ;-NP_CMD_01h causes always 8x7D

;mov a,02h // mov [002400h],a ;-NP_CMD_02h /WP=1 causes 2A,04,2A,2A instead of 2A,00,2A,2A --- and does set /WP=HIGH

;mov a,03h // mov [002400h],a ;-NP_CMD_03h /WP=0 no effect? but ONCE caused 2A,E0,2A,2A,FF,FF,FF,FF and /WP=LOW

;mov a,04h // mov [002400h],a ;-NP_CMD_04h HIROM:ALL ("MENU" at 40:7FC0h) causes FE,61,A5,00 instead of 03,AA,AA,00 ;and remaps ROM: eg. ..IJKL...RSTU... at 10FFC0h <-- part of GAME1 (though MENU is ar 407FC0)

mov a,05h // mov [002400h],a ;-NP_CMD_05h HIROM:MENU ("MENU" at 40:7FC0h) causes 83 D5 7F 00 instead of 03,AA,AA,00 ;and remaps ROM: all ................ at 10FFC0h (no ASCII) <-- MENU-only (if if GAME1 is selected)

;mov a,06h // mov [002400h],a ;-NP_CMD_06h causes always 8x7D (aka, undoes toggle?)

;mov a,07h // mov [002400h],a ;-NP_CMD_07h causes always 8x7D

;mov a,08h // mov [002400h],a ;-NP_CMD_08h causes always 8x7D

;mov a,09h // mov [002400h],a ;-NP_CMD_09h no effect ;\sending BOTH does have effect (remaps ROM) (happened only ONCE though)

;mov a,0ah // mov [002400h],a ;-NP_CMD_0ah no effect ;/

;mov a,0bh // mov [002400h],a ;-NP_CMD_0bh causes always 8x7D

;mov a,0ch // mov [002400h],a ;-NP_CMD_0ch causes always 8x7D

;mov a,0dh // mov [002400h],a ;-NP_CMD_0dh causes always 8x7D

;mov a,0eh // mov [002400h],a ;-NP_CMD_0eh causes always 8x7D

;mov a,0fh // mov [002400h],a ;-NP_CMD_0fh causes always 8x7D

;mov a,10h // mov [002400h],a ;-NP_CMD_10h causes always 8x7D

;mov a,14h // mov [002400h],a ;-NP_CMD_14h causes always 8x7D

;mov a,24h // mov [002400h],a ;-NP_CMD_24h causes always 8x7D

;mov a,44h // mov [002400h],a ;-NP_CMD_44h no effect (once caused crash with green rectange)

;mov a,81h // mov [002400h],a ;-NP_CMD_81h RESET and map GAME1 ;/

;mov a,84h // mov [002400h],a ;-NP_CMD_84h RESET and map GAME4 ;\works even if MENU was already deselected

;mov a,85h // mov [002400h],a ;-NP_CMD_85h RESET and map GAME5 ; odd: MENU in bank 48h, GAME1 in bank 50h (probably because BASE is FFh aka -1)

;mov a,89h // mov [002400h],a ;-NP_CMD_89h RESET and map GAME9 ;

;mov a,8fh // mov [002400h],a ;-NP_CMD_8Fh RESET and map GAME15 ;/

;mov a,0c5h // mov [002400h],a ;-NP_CMD_C5h causes always 8x7D

Some odd effects happened only once (that might have been unintended/unstable effects for whatever reason).

Some commands might do something when adding whatever parameters (eg. as known for commands 09h and 06h).

There stable/interesting commands are:

- 80h..8Fh: RESET and map GAME0..15 (aka 80h=MENU)

- 02h,03h: Controls /WP pin

- 04h/05h: Force HIROM mapping (either ALL memory, or only MENU)

With the "HIROM:ALL" command (04h) it should be possible to write the whole FLASH memory, so programming cartridges should be solved; unless there are some hidden configuration bits required for different games.

With different mappings (MENU, GAME's, or special HIROM modes), Port 2400h..2407h return different values (this on a cart with MENU and one 3MByte LOROM game (FIGHTING ELEVEN) installed):

Code:

;MENU: 2A,04,2A,2A,03,AA,AA,00

;GAME1: 2A,14,2A,2A,15,29,4A,10

;GAME4: 2A,44,2A,2A,FF,FF,FF,FF

;GAME5: 2A,54,2A,2A,FF,FF,FF,FF

;HIROM:ALL: 2A,04,2A,2A,FE,61,A5,00

;HIROM:MENU:2A,04,2A,2A,83,D5,7F,00

Port 2400h,2402h,2403h are always 2Ah.

Port 2401h.bit4-7 is the selected GAME number (or 0=MENU).

Port 2401h.bit2 is the /WP pin state.

Port 2404h..2407h are "strange values". The FFh's for the empty game slots would suggest that they are simply read somewhere from FLASH memory (either from the GAME memory, or from the DIRECTORY entries). For the other mappings, they are just "strange values", I can't find those values being stored anywhere in FLASH (at least not in continous 4-byte memory blocks, and they don't seem to match for separate bytes in the directory region).

Can somebody dump those values on other carts? Would be interesting if you are getting the same values.

Concerning hidden stuff, I have dumped the "sector protect" bytes for the MENU sectors, and for the first some sectors of the GAME.

The first sector (lorom banks 00h..03h) of the MENU returns C2h (which should mean "protected", although I

can write to that sector). The other three MENU sectors, and all GAME sectors are returning 00h (which should mean "unprotected") (and yes, writing to those sectors does work, too).

So, those bytes are apparently having a different meaning as described in the MX29F1610A/B datasheet. So they might contain hidden info about game mapping. Or they are just garbage because the "write protect" feature isn't implemented in MX29F1601 chip, though then it would be odd that different "write protect" have different values.

When dumping those bytes on other cartridges, are you getting the same results, first sector C2h, other sectors zero?

I added your findings to my MX29F1601 Arduino flasher, so it now can flash the complete NP cart without desoldering the flashroms, it's also alot faster than before.

This allowed me to do a couple of tests and it seems that the only thing that boots without a menu are games/programs that are 512K in size and lorom, like Super Mario World, the 240p Test Suite homebrew and ofc the NP menu.

Games like Super Bomberman(512K, hirom) or Super Mario Allstars(2M, lorom) won't boot.

I also flashed the japanese versions of DKC3(4M hirom) and Fire Emblem Thracia(4M lorom) and they didn't boot either even though they were available for the NP cart and Markfrizb stated that his DKC3 dump was identical to the retail rom.

On the other hand I flashed back the original content of my NP cart and that worked flawlessly, but then again it had a bootable menu.

So there must be a permanent hirom all/lorom all switch that can be toggled and if it's not the NP cart will just boot the 512k lorom menu or any other 512k lorom rom. Maybe some configuration bits are saved in the carts SRAM?

I'll try to write the suggested databus logger next to see what is happening right after powering up the NP cart.

sanni wrote:

I'll try to write the suggested databus logger next to see what is happening right after powering up the NP cart.

That would be great to see if/what kind of mapping info it's reading from FLASH (or SRAM) chips!

As far as I understood, mark has swapped FLASH chips with lorom/hirom games,

viewtopic.php?p=131832#p131832 so, theoretically, all mapping info should be located in the FLASH chip. The best candidate for hidden mapping info might be the 32 "sector protect" bytes for the 128Kbyte memory blocks. Would be interesting to dump those bytes, especially if somebody has a cart with a 4Mbyte hirom game on it.

skaman wrote:

when you were investigating the NP Ports 2400-2407, did you determine if Ports 2401-2407 were read-only?

My test cart was blank with only the Menu repeated 8x. I uploaded a new Menu along two new games but neither game works. Using the console, selecting the first game goes right back to the Menu. Selecting the second game results in a black screen. I experience the same results when using the reader with the reprogrammed cart, I can select the first game and it switches but right back to the Menu. If I select the second game, then the reader hangs waiting for the switch to occur (which never happens).

I then flashed the cart with FE776. Confirmed the flash was successful then I switched to the reader code. The reader starts up no problem with the reprogrammed cart. When I dumped the game, I got the first 512kb block of FE776 8x which exactly how the cart was mapped with the menu only.

Using CMD 0x5 on this Menu-only (blank) cart, I get: 2A,0,2A,2A,83,8A,8A,80

Carts with normal menus usually send: 2A,0,2A,2A,83,D5,7F,00

I've tested only writing to 2400h. The menu code is also writing to 2401h, so that should be writeable, too. Although, as one can see, the values writting to 2400h/2401h have no direct relation to the the values being returned when reading from 2400h/2401h, so it seems that there are read-only registers at 2400h/2401h, and separate write-only registers at 2400h/2401h. No idea if 2402h-2407h are also writeable.

What new menu and new games did you upload? If you've tried to create a custum menu with hand-edited directory entries, then you might have just screwed up that part - better would be dumping a working cart in HIROM:ALL mode to a 4Mbyte flash image, and then programming that image to another cart, in HIROM:ALL mode, too.

Btw. mind that the SNES memory map doesn't have FLASH/ROM in bank 7Eh-7Fh (ie. you can't access the whole hirom at 40h-7Fh), accessing the whole hirom should work in bank C0h-FFh.

On a blank cart, I would expect the menu being located in first 512K, and the remaining memory being FFh-filled. That, when using the HIROM:ALL mode for dumping the cart. If you are mapping game#0, or use the HIROM:MENU mode, then you would obviously see only the menu, repeated 8x aka mirrored throughout the whole memory space.

Currently, it does look as if there's some hidden mapping info required...

If it's in

SRAM, then you could simply copy the SRAM image alongsides with the FLASH image from one cart to another. That would be easy and worth testing, though it'd be a pretty bad design as it would brick the cartridge as soon as the battery becomes empty.

If there's an EEPROM in the

MX15001 chip, then one may need to send further stuff to port 2400h-2407h, which might be difficult: doing stuff like guessing how to enter the EEPROM programming sequence, and guessing which values being needed to be written to the EEPROM.

If it's in the

FLASH chip, then the "sector protect" bytes would still seem like the best candidates to me. Dumping those bytes would be easy as they are documented in the official datasheet, and from my tests, the chip does actually allow to read those bytes, but without actually using them for write-protection, so it wouldn't be unlikely that they are misused as mapping flags. Just DUMP those bytes, and check if you get different values on different carts! Somewhat like so:

Code:

after entering HIROM:ALL mode...

[C0AAAAh]=AAh ;\for 1st flash chip:

[C05554h]=55h ; enter read chip id / read sector protect mode

[C0AAAAh]=90h ;/

[E0AAAAh]=AAh ;\for 2nd flash chip:

[E05554h]=55h ; enter read chip id / read sector protect mode

[E0AAAAh]=90h ;/

for i=0 to 1Fh

DisplayHexValue([C00004h+i*20000h]) ;display sector protect bytes

next i

On my cart, the first byte would be C2h, followed by 00h-bytes.

I tried the SRAM theory, sadly it was a dead end. Even after I flashed both the SRAM and the complete 4MB dump of skaman's Fire Emblem NP cart to my former menu+DerbyStallion98 cart it didn't boot.

I also tried listening to the databus with the Arduino but I'm not sure if I'm doing it right.

To me it looks like the MX15001 chip is resetting the flash and then doing some other stuff and sometimes it then resets the flash a second time.

In case it matters, I removed the CIC and all clocks for this test, and just manually clocked the expclk pin with a pin from the arduino, maybe about 500-700khz 50% duty cycle or something like that.

And the NP cart is a working Menu+Derby Stallion 98.

Writing and reading the complete NP cart also works this way.

Code:

(0)Menu 0x80

Data: 0x2A Reset: 1

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0x55 Reset: 0

Data: 0xF0 Reset: 0

Data: 0x38 Reset: 0

Data: 0xD0 Reset: 0

Data: 0x71 Reset: 0

Data: 0x88 Reset: 0

Data: 0xFF Reset: 0

Data: 0x72 Reset: 0

Data: 0x75 Reset: 0

Data: 0x3 Reset: 0

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0xFF Reset: 0

Data: 0x0 Reset: 0

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0x55 Reset: 0

Data: 0xF0 Reset: 0

Data: 0x7D Reset: 1

Somtimes it does the same but without second flash reset

Code:

(0)Menu 0x80

Data: 0x2A Reset: 1

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0x55 Reset: 0

Data: 0xF0 Reset: 0

Data: 0x38 Reset: 0

Data: 0xD0 Reset: 0

Data: 0x71 Reset: 0

Data: 0x88 Reset: 0

Data: 0xFF Reset: 0

Data: 0x72 Reset: 0

Data: 0x75 Reset: 0

Data: 0x3 Reset: 0

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0xFF Reset: 0

Data: 0x0 Reset: 0

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0x7D Reset: 1

"Hirom All" and "hirom menu" don't do any reset, it's just 0x2A all the time with them

Code:

(1)GAME1 0x81

Data: 0x2A Reset: 1

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0x55 Reset: 0

Data: 0xF0 Reset: 0

Data: 0x38 Reset: 0

Data: 0xD0 Reset: 0

Data: 0x71 Reset: 0

Data: 0x88 Reset: 0

Data: 0xFF Reset: 0

Data: 0x72 Reset: 0

Data: 0x75 Reset: 0

Data: 0x16 Reset: 0

Data: 0xFF Reset: 0

Data: 0x29 Reset: 0

Data: 0xFF Reset: 0

Data: 0x4A Reset: 0

Data: 0xFF Reset: 0

Data: 0x10 Reset: 0

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0x55 Reset: 0

Data: 0xF0 Reset: 0

Data: 0x7D Reset: 1

Code:

(2)GAME2 0x82

Data: 0x2A Reset: 1

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0x55 Reset: 0

Data: 0xF0 Reset: 0

Data: 0x38 Reset: 0

Data: 0xD0 Reset: 0

Data: 0x71 Reset: 0

Data: 0x88 Reset: 0

Data: 0xFF Reset: 0

Data: 0x72 Reset: 0

Data: 0x75 Reset: 0

Data: 0xFF Reset: 0

Data: 0xAA Reset: 0

Data: 0x55 Reset: 0

Data: 0xF0 Reset: 0

Data: 0x7D Reset: 1

Cool, many thanks! That values do actually make sense: They seem to be the standard FLASH read/reset commands (as you said), plus additional Satellaview-style custom extra FLASH commands for reading the per-game mapping info from the FLASH chip.

Arranging your four dumps next to each other:

Code:

Menu 0x80 Menu 0x80 GAME1 0x81 GAME2 0x82

Data: 0x2A Data: 0x2A Data: 0x2A Data: 0x2A Reset: 1 ;-Port 2400h (before /RESET)

Data: 0xFF Data: 0xFF Data: 0xFF Data: 0xFF Reset: 0 ;-HighZ

Data: 0xAA Data: 0xAA Data: 0xAA Data: 0xAA Reset: 0 ;\

Data: 0x55 Data: 0x55 Data: 0x55 Data: 0x55 Reset: 0 ; FLASH read/reset command

Data: 0xF0 Data: 0xF0 Data: 0xF0 Data: 0xF0 Reset: 0 ;/

Data: 0x38 Data: 0x38 Data: 0x38 Data: 0x38 Reset: 0 ;\

Data: 0xD0 Data: 0xD0 Data: 0xD0 Data: 0xD0 Reset: 0 ; FLASH request chip info part 1

Data: 0x71 Data: 0x71 Data: 0x71 Data: 0x71 Reset: 0 ;/

Data: 0x88 Data: 0x88 Data: 0x88 Data: 0x88 Reset: 0 ;-Read Ready-status (bit7=1=ready)

Data: 0xFF Data: 0xFF Data: 0xFF Data: 0xFF Reset: 0 ;-HighZ

Data: 0x72 Data: 0x72 Data: 0x72 Data: 0x72 Reset: 0 ;\FLASH request chip info part 2

Data: 0x75 Data: 0x75 Data: 0x75 Data: 0x75 Reset: 0 ;/

Data: 0x3 Data: 0x3 Data: 0x16 Data: 0xFF Reset: 0 ;-Read value for Port 2404h

Data: 0xFF Data: 0xFF Data: 0xFF - Reset: 0 ;-HighZ

Data: 0xAA Data: 0xAA Data: 0x29 - Reset: 0 ;-Read value for Port 2405h

Data: 0xFF Data: 0xFF Data: 0xFF - Reset: 0 ;-HighZ

Data: 0xAA Data: 0xAA Data: 0x4A - Reset: 0 ;-Read value for Port 2406h

Data: 0xFF Data: 0xFF Data: 0xFF - Reset: 0 ;-HighZ

Data: 0x0 Data: 0x0 Data: 0x10 - Reset: 0 ;-Read value for Port 2407h

Data: 0xFF Data: 0xFF Data: 0xFF - Reset: 0 ;-HighZ and/or TERMINATE status mode

Data: 0xAA Data: 0xAA Data: 0xAA Data: 0xAA Reset: 0 ;\

Data: 0x55 - Data: 0x55 Data: 0x55 Reset: 0 ; FLASH read/reset command

Data: 0xF0 - Data: 0xF0 Data: 0xF0 Reset: 0 ;/

Data: 0x7D Data: 0x7D Data: 0x7D Data: 0x7D Reset: 1 ;-Port 2400h (after /RESET)

The leading/ending 2Ah/7Dh values seem to be just read from Port 2400h (assuming that you are still outputting address 2400h on address bus, as a relict from the preceeding Port 2400h game selection write) (and assuming that you have /OE switched LOW for some reason).

The AAh,55h,F0h values are just resetting the FLASH chip to read mode.

The 38h,D0h,71h, and 72h,75h values are custom FLASH commands, exactly same as used for Satelleview FLASH cart chip detection (though in this case they seem to be used for reading mapping info, not for chip detection).

The various FFh-bytes are probably just HighZ (at least most of them) occuring for a short moment when neither /OE nor /WE is output to the FLASH chip (yesterday you had posted a "dirtier" dump that showed each value repeated several times, and the FFh's were repeated only 2 times, unlike as the other values which occurred repeated 6-8 times). Looking at the above table, it does look as if the FFh/HighZ's do occur after READing from FLASH chip, so they do help on guessing the Read/Write-direction of the separate bytes.

The last FFh byte might be just another HighZ... or, if occurs for a longer duration, then it would be probably a FFh value written to terminate the chip-info mode (as done by satellaview).

The 88h byte being read after the writing 38h,D0h,71h seems to be just a status byte with bit7=ready, the Satellaview bios is reading that kind of status value in that place, too.

The remaining four bytes are supposedly mapping info being read from the chip, and then copied to port 2404h-2407h.

The missing two bytes in the second dump: That looks as if something went wrong, either your dumping software missed the 55h,F0h bytes, or the MX150001 chip somehow failed to output those bytes; maybe related to absent CIC. Anyways, just let's ignore that.

The missing seven bytes in the fourth dump: As there's no GAME2 on that cart, two things could have happened: The chip did output four FFh bytes (plus four HighZ bytes) in that case you should see about thirty-two repeated FFh's. Or the chip did output only one FFh byte, and the MX150001 did treat that as "no game" and aborted reading the other bytes.

For the address bus values, the AAh,55h,F0h values are obviously written to standard FLASH addresses (AAAAh and 5554h). The 38h,D0h,71h, and 72h,75h bytes are probably just written to FLASH address 0000h (the satellaview bios is doing it that way), the 88h ready byte is probably read from address 0002h (also as done by satellaview), and the four mapping bytes are probably read somewhere from FF00h..FFxxh (also as done by satellaview, but in this case using different addresses based on the preceeding port 2400h game selection).

Next steps should be:

Trying to read the mapping info manually from the FLASH chips.

Somehow "decrypt" those values & figure out which bits do affect the ROM/SRAM mapping base/size and lorom/hirom mode. For that purpose, it would be helpful to collect mapping bytes from different nintendo power carts.

And try to erase/rewrite the mapping bytes via whatever FLASH commands, which may require some guessing or brute forcing. Or, as skaman asked if port 2404h-2407h are write-able: That might be also worth trying. If it works then one could completely bypass the hidden mapping bytes, and just use a custom menu which is manually applying the mapping based on the directory and cart-header's (instead of using the [002400h]=8xh game selection).

Tried to write port 2401h..2407h: It didn't change any values read from 2400h..2407h, so that ports aren't writeable (or writing works only indirectly in form of command parameters, as done with port 2401h during initialization).

And, tried dumping the hidden memory of my menu+fighting eleven cart, that worked well:

Code:

menu+fighting eleven - chip 1:

C0FF00 03 11 AA 50 AA 98 00 10 ;Menu (512Kbyte Lorom)

C0FF08 15 25 29 05 4A 47 10 54 ;Fighting Eleven (3072Kbyte Lorom, 8Kbyte SRAM)

C0FF10 FF FF FF FF FF FF FF FF ;unused

... FF FF FF ... ;...

C0FFF8 FF FF FF FF FF FF FF FF ;unused

menu+fighting eleven - chip 2:

E0FF00 FF FF FF FF FF FF FF FF

... FF FF FF ...

E0FF88 FF FF FF FF FF FF FF FF

E0FF90 FF FF 55 00 FF FF FF FF ;<--

E0FF98 FF FF FF FF FF FF FF FF

E0FFA0 FF FF FF FF FF FF 55 00 ;<--

E0FFA8 FF FF FF FF FF FF FF FF

E0FFB0 FF FF FF FF FF FF 00 00 ;<--

E0FFB8 FF FF FF FF FF FF FF FF

... FF FF FF ...

E0FFF8 FF FF FF FF FF FF FF FF

The bytes at even addresses are the values for port 2404h..2407h (eg. 03,AA,AA,00 for menu). Confusingly there are further values at odd addresses (eg. 11,50,98,10 for menu). Going by sanni's databus dump that values aren't used during game selection, so they seem to be just unused garbage... unless they are checked on power-up, or are used internally by the FLASH chip for whatever purpose.

The data repeats every 100h bytes. The satellaview uses address 0FFxxh, but one could as well read anywhere from 000xxh to 1FFxxh. Assuming that the whole 100h bytes are writeable, then the whole mapping info for ALL games will be probably stored in the first chip, and the other 100h bytes in second chip would be always FFh-filled (apart from those 55h/00h values seen in above dump, which might be some chip-testing relicts or so).

The dumping function looks as so:

Code:

mov a,038h // mov [far 0c00000h],a

mov a,0d0h // mov [far 0c00000h],a

mov a,071h // mov [far 0c00000h],a

mov a,[far 0c00004h] // call wrhexa // call wrcrlf ;<-- addr=4 required (unlike satellaview's addr=2)

mov a,072h // mov [far 0c00000h],a

mov a,075h // mov [far 0c00000h],a

mov x,0

@@show_hidden_info_ylop:

mov a,x

call wrhexa

call wrspc

@@show_hidden_info_xlop:

call wrspc

mov a,[far 0c0ff00h+x+0h] // call wrhexa ;this data repeats every 100h bytes (at C000xxh..DFFFxxh)

inc x

mov a,x

and a,07h

jnz @@show_hidden_info_xlop

call wrcrlf

cmp x,00h ;aka 100h when using non-8bit maths

jnz @@show_hidden_info_ylop

mov a,0ffh // mov [far 0c00000h],a ;<-- no effect (use below AAAAh/5554h/AAAAh stuff instead)

mov a,[far 0c00000h] // call wrhexa // call wrcrlf ;still returns HIDDEN data

mov a,0aah // mov [far 0c0aaaah],a ;\

mov a,055h // mov [far 0c05554h],a ; return to normal read mode

mov a,0f0h // mov [far 0c0aaaah],a ;/

mov a,[far 0c00000h] // call wrhexa // call wrcrlf ;returns normal FLASH data

For the second chip use address E0xxxxh instead C0xxxxh. Switch to HIROM:ALL mode before using above function.

Wow so much info, thank you, I read through it three times already and am still amazed. This is one very interesting cartridge.

Got some more mapping bytes from skaman:

Code:

;------------------

blank cart (menu only):

C0FF00 03 11 AA 56 AA 97 00 11 ;Menu (512Kbyte Lorom)

C0FF08 00 25 00 10 00 25 00 02 ;empty (no game installed)

C0FF10..FF FF-filled

E0FF00..8F FF-filled