I wanted to try and RE the CIC, but have found little info on it. I know some guys were trying to get the source code using an electron microscope. I'd rather not go this route because it would be no different than getting the source from the patent like tengen did. Has any one ever tried to data log the communications between the key and lock? Maybe we could lower the clock speed to make it easier to log. This is just speculation on how I think it could work. I'm thinking that the Lock sends a number to the Key, then they both use this as the seed for some alogarithim or random number generator. After so many clock cycles the key sends it's results to the lock. The lock then compares it with what it calculated and responds accordingly. Does this sound feasible? Or am I way off track. Not having a CIC replacement is one of our biggest barriers in developing new games, so we need to crack this thing. Any suggestion would be greatly appreciated.

My understanding is that the two CIC chips run identical programs and continually communicate some portion of their state between each other. If these communications differ, the NES goes into reset mode. I heard that someone once tried to log these communications, but even after hundreds of megabytes of data there was no repetition.

The electron microscope route to uncover the source code would not ultimately be to merely copy the source code, but to reverse-engineer it and write new code (for something more modern like a PIC microcontroller) that gives the same result as the original CIC code.

It's funny that modern encryption schemes like CSS and the like have been broken, but this ancient copy protection chip is still a mystery.

The electron microscope route to uncover the source code would not ultimately be to merely copy the source code, but to reverse-engineer it and write new code (for something more modern like a PIC microcontroller) that gives the same result as the original CIC code.

It's funny that modern encryption schemes like CSS and the like have been broken, but this ancient copy protection chip is still a mystery.

Something to look into.. Has patent protection expired on this? It must have been more than 20 years since the patents were filed. Not knowing much about these things, I would expect the patent protection to last for about 15 years. If the protection has expired, then perhaps it wouldn't be necessary to be selective in your methods.

I'm not against the SEM I just want to take a different approach.

Perhaps whoever tried datalogging it either wasn't thorough or maybe this thing needs a different approach. What if we just take a small sample and then try to find alogarithms that will produce the same output. It probably wouldn't take much to narrow down one that is the same. Assuming it is a 4bit MPU and we know for sure it's clock is 4Mhz. It can only perform so many operations. It probably transfers 1 or more nibbles at a time. For each nibble added the possibilites increase but it also reduces the amount of operations it can perform on it. When you take into account the 1hz square wave it outputs for reset. That only leaves 1s to apply an alogarithm. Not to mention the MPU probably takes multiple clock cycles per instruction. Any ideas on making a 2bit data logger?

Perhaps whoever tried datalogging it either wasn't thorough or maybe this thing needs a different approach. What if we just take a small sample and then try to find alogarithms that will produce the same output. It probably wouldn't take much to narrow down one that is the same. Assuming it is a 4bit MPU and we know for sure it's clock is 4Mhz. It can only perform so many operations. It probably transfers 1 or more nibbles at a time. For each nibble added the possibilites increase but it also reduces the amount of operations it can perform on it. When you take into account the 1hz square wave it outputs for reset. That only leaves 1s to apply an alogarithm. Not to mention the MPU probably takes multiple clock cycles per instruction. Any ideas on making a 2bit data logger?

Such a data logger has already been made by kevtris, and the data stream is extremely sparse - short bursts of '1' (each 3 clocks long) followed by huge spans of '0' (ranging from 76 to well over ten thousand).

Note that the CIC is clocked at 4MHz, but the clock is effectively divided by 4, resulting in two 1MHz data streams.

Note that the CIC is clocked at 4MHz, but the clock is effectively divided by 4, resulting in two 1MHz data streams.

If you write your own original program that performs the same function, then you are not violating the copyright, but you may be violating the patent. The patent has expired (filing + 20), but the copyright has not.

The biggest obstacle to CIC RE right now is the unknown 1. instruction set architecture and 2. layout of addresses in the internal ROM.

The biggest obstacle to CIC RE right now is the unknown 1. instruction set architecture and 2. layout of addresses in the internal ROM.

I dont think looking at the data stream is the solution, mainly because I have tried and failed =] Atari/Tengen also tried and failed. They eventually decapped the chip. I am waiting for ~6 more lockout chip versions to be decapped from neviksti, the same guy that did the other one on cherryroms. I am hoping the roms from all of them can be compared to get more architecture info. So far none of the permutations/inversions of the rom data match any Sharp instruction sets I have found.

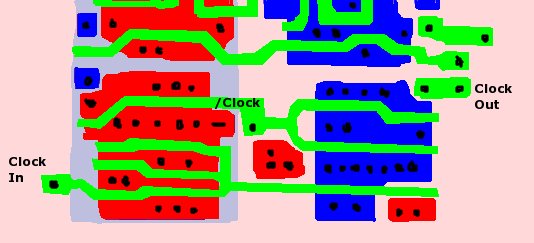

If you want to look at the stream there is some important starting information. First is the bit rate is not as described on the patent info. This will be shown in the picts below. Second is there are only 16 unique streams, selected by the cic chip in the nes at the beginning. Each stream is apparently non repeating and constant, so record/playback is not an option. The data stream is very sparse with long and VERY long pauses between pulses.

Here is what I have learned so far, gathered from a usa nes-cpu-11 + logic analyzer. I connected directly to the cic in the nes, so dout is to cart and din is from cart. Ignore clock in all pictures except for the close up of the pulse. The first transaction syncs the chips using resetout line from nes->cart. Then the nes selects 1 of 16 streams, shown in the first 4 pulses. The length and pause between those pulses is shown close up. The clock does not seem to match the patents. After that the bits transferred are always the same, and resetnes goes high when the cart is authenticated ~1300uS later. When there is no cart, some bits are missing and resetnes stays low and starts the 1hz sequence. Now comes the sparse part. There is nothing for ~2.5mS, then a second transaction. All 16 possible second transactions are shown. I was hoping it was send 16 bits, wait 2.5mS, send 16 bits, etc but that doesnt line up later. The data transfers just keep going and are similarly sparse. Disconnecting either din or dout at any time causes it to go into reset so both chips are still looking for input from the other.

If I ever get some more free time I can capture more sequences, and also look at the protocol of the other country lockouts. I am guessing the other country ones just switch around what number each stream is.

If you want to look at the stream there is some important starting information. First is the bit rate is not as described on the patent info. This will be shown in the picts below. Second is there are only 16 unique streams, selected by the cic chip in the nes at the beginning. Each stream is apparently non repeating and constant, so record/playback is not an option. The data stream is very sparse with long and VERY long pauses between pulses.

Here is what I have learned so far, gathered from a usa nes-cpu-11 + logic analyzer. I connected directly to the cic in the nes, so dout is to cart and din is from cart. Ignore clock in all pictures except for the close up of the pulse. The first transaction syncs the chips using resetout line from nes->cart. Then the nes selects 1 of 16 streams, shown in the first 4 pulses. The length and pause between those pulses is shown close up. The clock does not seem to match the patents. After that the bits transferred are always the same, and resetnes goes high when the cart is authenticated ~1300uS later. When there is no cart, some bits are missing and resetnes stays low and starts the 1hz sequence. Now comes the sparse part. There is nothing for ~2.5mS, then a second transaction. All 16 possible second transactions are shown. I was hoping it was send 16 bits, wait 2.5mS, send 16 bits, etc but that doesnt line up later. The data transfers just keep going and are similarly sparse. Disconnecting either din or dout at any time causes it to go into reset so both chips are still looking for input from the other.

If I ever get some more free time I can capture more sequences, and also look at the protocol of the other country lockouts. I am guessing the other country ones just switch around what number each stream is.

tepples wrote:

The biggest obstacle to CIC RE right now is the unknown 1. instruction set architecture and 2. layout of addresses in the internal ROM.

I agree, and I think the unknown ISA is the biggest of the problems. Using Nevitski's pictures I have transcoded the binary for the code. However, this is useless without knowing the instruction set. I haven't gone so far as to try to map it to the Sharp chips, but it looks like bunnyboy has done so. If there are any crypto experts out there that could take the info we have and turn it into a number crunching excercise that would be great. I'm sure we can round up enough cpu cycles to solve it, the problem is framing the question so that this approach can be tried.

Thanks for all the info above. It should save me considerable time. I'm glad to see that I'm not the only one bothered by this unsolved mystery.

I pulled a couple CIC's off some carts and stuck them in a bread board. I don't have a logic probe so I'm just going to use the parallel port on my computer. I did some experiments and found that they still function @ 100Khz clock speed.

Do you think that the Lock selecting one of the 16 streams is the seed for the key to use as a number generator? If so than maybe analyzing all the streams together would make cracking the code easier.

I read the cherryrom forum about extracting the rom. Did anyone ever consider trying to make the ISA from scratch? Perhaps write a program to emulate a cpu that can easily swap out instruction sets. Then just let it cycle through all the different ones untill it outputs something that resembles the data streams. Could someone give me the link to the binary of the rom?

I pulled a couple CIC's off some carts and stuck them in a bread board. I don't have a logic probe so I'm just going to use the parallel port on my computer. I did some experiments and found that they still function @ 100Khz clock speed.

Do you think that the Lock selecting one of the 16 streams is the seed for the key to use as a number generator? If so than maybe analyzing all the streams together would make cracking the code easier.

I read the cherryrom forum about extracting the rom. Did anyone ever consider trying to make the ISA from scratch? Perhaps write a program to emulate a cpu that can easily swap out instruction sets. Then just let it cycle through all the different ones untill it outputs something that resembles the data streams. Could someone give me the link to the binary of the rom?

I put all my text files in a new directory at www.nesmuseum.com/10nes It has been a few weeks since I looked at all this so I'm not sure I remember what all of them are so use carefully....

D411_rom.txt - snes lockout rom dump, directly from rom array. snes has same chip, different rom

nescicrom.txt - nes lockout rom dump, directly from rom array. Bits and bytes are interleaved, figuring out how it is actually arranged is part of the problem.

nescicromuninterleaved.txt - uninterleaved data in the way I believe it is arranged. Split into top half (I think data) and bottom half (I think code).

romhex-le-inv.txt - uninterleaved, written in hex, little endian bits (i think). inv probably refers to whether the black in the rom pictures are a 0 or a 1.

romhexsn-le-inv.txt - not sure what the sn means compared to other hex file, could be rotating the bits 90 degrees...

popcount-bot.txt - this is an attempt to see how often bytes appear to guess at instruction sets. bot means only the second half of the rom is counted. The large amount of FF or 00 without it being in a solid block is somewhat confusing.

popcount-le-inv-bot.txt - same as above, but little endian bits. doesnt change the FF or 00 problem.

I also tried to find repeating consecutive byte pairs but there was nothing significant. I think there are similarities between nes and snes rom but not in anything bigger than 2 bytes in a row. My brother wrote all the manipulation programs so I should be able to get them from him and make them available, but he is gone for a few more days. He also wrote a quick disasm app for some of the Sharp instruction sets I found but they didnt make sense in any bit arrangements.

One method that might be interesting is to look at the Tengen cic clone. It has the Motorola logo on it so hopefully it is a standard cpu core from them. I sent one to be decapped and hopefully rom dumped. Would be much easier to match to common core like 680x instead of guessing at the entire architecture. Anyone know of a good source of images of the 6800 core? I am actually surprised none of the Tengen info has been found or leaked out.

D411_rom.txt - snes lockout rom dump, directly from rom array. snes has same chip, different rom

nescicrom.txt - nes lockout rom dump, directly from rom array. Bits and bytes are interleaved, figuring out how it is actually arranged is part of the problem.

nescicromuninterleaved.txt - uninterleaved data in the way I believe it is arranged. Split into top half (I think data) and bottom half (I think code).

romhex-le-inv.txt - uninterleaved, written in hex, little endian bits (i think). inv probably refers to whether the black in the rom pictures are a 0 or a 1.

romhexsn-le-inv.txt - not sure what the sn means compared to other hex file, could be rotating the bits 90 degrees...

popcount-bot.txt - this is an attempt to see how often bytes appear to guess at instruction sets. bot means only the second half of the rom is counted. The large amount of FF or 00 without it being in a solid block is somewhat confusing.

popcount-le-inv-bot.txt - same as above, but little endian bits. doesnt change the FF or 00 problem.

I also tried to find repeating consecutive byte pairs but there was nothing significant. I think there are similarities between nes and snes rom but not in anything bigger than 2 bytes in a row. My brother wrote all the manipulation programs so I should be able to get them from him and make them available, but he is gone for a few more days. He also wrote a quick disasm app for some of the Sharp instruction sets I found but they didnt make sense in any bit arrangements.

One method that might be interesting is to look at the Tengen cic clone. It has the Motorola logo on it so hopefully it is a standard cpu core from them. I sent one to be decapped and hopefully rom dumped. Would be much easier to match to common core like 680x instead of guessing at the entire architecture. Anyone know of a good source of images of the 6800 core? I am actually surprised none of the Tengen info has been found or leaked out.

Quote:

Did anyone ever consider trying to make the ISA from scratch? Perhaps write a program to emulate a cpu that can easily swap out instruction sets. Then just let it cycle through all the different ones untill it outputs something that resembles the data streams.

Interesting idea, almost like the Superoptimizer from years ago, which tried every sequence of several instructions to find the shortest one to carry out the desired operation.

One problem is, there are probably many instruction sets that would carry out the beginning correctly, but fail at some point due to the code relying on features at different times (i.e. carry or something).

bunnyboy wrote:

One method that might be interesting is to look at the Tengen cic clone. It has the Motorola logo on it so hopefully it is a standard cpu core from them. I sent one to be decapped and hopefully rom dumped. Would be much easier to match to common core like 680x instead of guessing at the entire architecture. Anyone know of a good source of images of the 6800 core? I am actually surprised none of the Tengen info has been found or leaked out.

I agree, this sounds like the most promising approach. This was discussed over at CherryRoms a long time ago though, I figured the effort had been given up. Glad to see it's still in process. When you get the SEM photo's back please let us know, I'm not too bad with reading them.

Zack S: I noticed you added some of this information to the old NESdev wiki - you really should be adding this sort of stuff to the new wiki (currently hosted at http://nesdevwiki.ath.cx/) so we don't have to add it to the list of stuff to copy over.

I didn't realize there was a new wiki. I'll move everything over to it. Also does anyone know excactly what pins 11 to 15 are? I remember Kevin saying something about them being used address up to 16 on the same bus. This would require a 4bit address bus. Perhaps one of the five is a /CE input and the rest are /A[0..3]. I would think since they all are active low they should all be interchangable.

I just got 4 more college classes today so I might not have time to get to data logging anytime soon. Eventually I will though. Even if I can't crack the code, figuring out as much about it's operation as possible should make the ROM extracting much easier. It could even give insight on how the internals of the chip might work.

I just got 4 more college classes today so I might not have time to get to data logging anytime soon. Eventually I will though. Even if I can't crack the code, figuring out as much about it's operation as possible should make the ROM extracting much easier. It could even give insight on how the internals of the chip might work.

So, can some of this be translated into newbie? There are only 16 codes. Looking at some of the pictures above, they seem to be the same total length. How many bits or bytes long are they? Are there 16 total, or are there 16 sends and 16 replies? Is that all there is in a cycle?

You don't have to, but and explantion of how to read green squiggily lines would be great! I'm assuming that each bump on the 16 picture is 3 ones in bianary? The scale seems to go from -700 to 700. Does this mean 1,400 bits?

Are both chips sending at the same time or does one start a sending pattern and the other one start a reply? Is the first half of one of the sixteen transmissions a send and the second half a reply or something?

So there's very long lengths of zeros. What's the highest comon denominator?

You don't have to, but and explantion of how to read green squiggily lines would be great! I'm assuming that each bump on the 16 picture is 3 ones in bianary? The scale seems to go from -700 to 700. Does this mean 1,400 bits?

Are both chips sending at the same time or does one start a sending pattern and the other one start a reply? Is the first half of one of the sixteen transmissions a send and the second half a reply or something?

So there's very long lengths of zeros. What's the highest comon denominator?

bunnyboy: how fast is your logic analyzer clocking at?

The 16 codes means there are 16 streams of never ending, never repeating data. We have no idea how long in bits or time one transfer is. We also dont know if the bits represent values. The protocol could be running a timer and counting the clocks between high bits. The 16 rows in the second transactions picture are just a small section of each of the 16 possible streams. I think they are arranged logically so stream 0 is first, then stream 1, then stream 2, etc.

On the pictures: a line up means 5 volts, logic 1. Line down means 0 volts, logic 0. The numbers at the top (-600uS, 300uS, etc) are the time scale, relative to the center of the screen. We dont know how fast the bit rate is, so 600uS != 600 bits. Any number with a T in it (T, T+676uS, T+2.8mS, etc) is relative to the trigger, which in this case is the beginning of the sync pulse. This shows in the second transaction picture that everything is happening ~2.5mS after the sync pulse.

The bit transfers are slightly shifted, with the nes cic sending before the cart cic sends. You can see them shifted 1-2 pixels which is probably 1-2 clock cycles. Most likely the nes cic sends then receives, the cart cic receives then sends

The logic analyzer runs at up to 500MHz, I usually use 100MHz which very easily captures everything accurately. The pictures are just screenshots so its not easy to get long sequences. I can also save state transition tables but I do not know of a good program to view those. It would help lots, anyone know of one? Sample state transition table: 10nes.csv

Just to make this post even longer, here is a bit more information about the initial transaction. One of the bits in the stream select triggers the first bit received from the cart. I dont remember which stream bit it was tho... Here is a picture with some stuff circled. All other bits are always the same until the reset line goes high. Once again ignore the clock in the picture.

On the pictures: a line up means 5 volts, logic 1. Line down means 0 volts, logic 0. The numbers at the top (-600uS, 300uS, etc) are the time scale, relative to the center of the screen. We dont know how fast the bit rate is, so 600uS != 600 bits. Any number with a T in it (T, T+676uS, T+2.8mS, etc) is relative to the trigger, which in this case is the beginning of the sync pulse. This shows in the second transaction picture that everything is happening ~2.5mS after the sync pulse.

The bit transfers are slightly shifted, with the nes cic sending before the cart cic sends. You can see them shifted 1-2 pixels which is probably 1-2 clock cycles. Most likely the nes cic sends then receives, the cart cic receives then sends

The logic analyzer runs at up to 500MHz, I usually use 100MHz which very easily captures everything accurately. The pictures are just screenshots so its not easy to get long sequences. I can also save state transition tables but I do not know of a good program to view those. It would help lots, anyone know of one? Sample state transition table: 10nes.csv

Just to make this post even longer, here is a bit more information about the initial transaction. One of the bits in the stream select triggers the first bit received from the cart. I dont remember which stream bit it was tho... Here is a picture with some stuff circled. All other bits are always the same until the reset line goes high. Once again ignore the clock in the picture.

bunnyboy wrote:

We also dont know if the bits represent values. The protocol could be running a timer and counting the clocks between high bits.

What is the distribution of clocks between high bits? If someone could make a histogram out of the CSV file, that would be nice. Then we could tell if it's counting the clocks (for example: generate number, wait that many cycles, output 1, output 0) or if it's comparing (for example: generate number, if equal to 0 output 1 else output 0). If the time between 1's is roughly uniformly distributed, it's generating and waiting; if it's non-uniform, it's generating constantly and comparing.

Quote:

The logic analyzer runs at up to 500MHz, I usually use 100MHz which very easily captures everything accurately.

Could you go down to 32 MHz or 16 MHz for some captures so that you can get more data at once while still appreciably oversampling to remove aliasing artifacts? Does your analyzer support synchronizing to a multiple of the CIC clock, or must it always run asynchronously?

tepples wrote:

What is the distribution of clocks between high bits? If someone could make a histogram out of the CSV file, that would be nice. Then we could tell if it's counting the clocks (for example: generate number, wait that many cycles, output 1, output 0) or if it's comparing (for example: generate number, if equal to 0 output 1 else output 0). If the time between 1's is roughly uniformly distributed, it's generating and waiting; if it's non-uniform, it's generating constantly and comparing.

I think it will be a bit harder than that because of the apparent chunks of important data. It looks like there is a big pause then a set of 1/0s then another big pause. I will have to capture more data....

tepples wrote:

Could you go down to 32 MHz or 16 MHz for some captures so that you can get more data at once while still appreciably oversampling to remove aliasing artifacts? Does your analyzer support synchronizing to a multiple of the CIC clock, or must it always run asynchronously?

When I run the analyzer fast I have compression which means only state transitions are stored. Number of transitions is the limit, not time (which is why I dont capture the clock signal). I havent played with other modes but I should be able to capture everything for long periods of time. The parallel port to control clock signal would probably be better at that tho.

I can do synchronous but only on transitions of one direction and I think important stuff happens on rising and falling edges of the clock.

I really want to get theese things hooked up to a Parallel port. I'll try to do it this weekend. Anybody prefer I store the data a certian way?

I was thinking of just making a list of numbers the first number is how many clock cycles low, then keep alternating back and forth. This would greatly reduce the file size and I would think be pretty easy to analize. It would look like this: 1,2,4,1 would represent LHHLLLLH. L and H being low and high respectively.

I like bunnyboys approach to how this thing works. I was thinking it probably counts the clock cycles to hold Dout low too. Also perhaps the meaningfull data is simply the next random number. It could alternate between using the random number to output clock cycles and then it takes the next random number and just sends it's value serially. Just a guess though.

If it does generate random numbers then it's possible the Lock sends the seed as it's method of stream selection. I hope this is the case, cause then we can simulate a lock chip and send it different seeds. Sending all zeros for a seed would show us if any of the bits are ORed or XORed. All ones could reveal possible AND and XOR instructions. If anyone's intrested in using the parallel port to gather info, but doesn't have the low level digital electronics knowledge to set it up let me know and I will post my schematics and the source code too, as soon as I get it working good.

I was thinking of just making a list of numbers the first number is how many clock cycles low, then keep alternating back and forth. This would greatly reduce the file size and I would think be pretty easy to analize. It would look like this: 1,2,4,1 would represent LHHLLLLH. L and H being low and high respectively.

I like bunnyboys approach to how this thing works. I was thinking it probably counts the clock cycles to hold Dout low too. Also perhaps the meaningfull data is simply the next random number. It could alternate between using the random number to output clock cycles and then it takes the next random number and just sends it's value serially. Just a guess though.

If it does generate random numbers then it's possible the Lock sends the seed as it's method of stream selection. I hope this is the case, cause then we can simulate a lock chip and send it different seeds. Sending all zeros for a seed would show us if any of the bits are ORed or XORed. All ones could reveal possible AND and XOR instructions. If anyone's intrested in using the parallel port to gather info, but doesn't have the low level digital electronics knowledge to set it up let me know and I will post my schematics and the source code too, as soon as I get it working good.

Zack S wrote:

If it does generate random numbers then it's possible the Lock sends the seed as it's method of stream selection. I hope this is the case, cause then we can simulate a lock chip and send it different seeds. Sending all zeros for a seed would show us if any of the bits are ORed or XORed.

Yeah right. I'd bet it looks up the seed in a table.

tepples wrote:

Yeah right. I'd bet it looks up the seed in a table.

You shot that idea down pretty quick. I bet you're right though. None the less I'll still check.

Quote:

I was thinking of just making a list of numbers the first number is how many clock cycles low, then keep alternating back and forth. This would greatly reduce the file size and I would think be pretty easy to analize. It would look like this: 1,2,4,1 would represent LHHLLLLH. L and H

Use something that isn't so fragile. How about the format of the logs posted, where they are composed of state snapshots with the delays between them?

As for the algorithm, it could be quite complex and not at all simple to understand. As long as it's deterministic, they could just throw random code together with some design. They were smart to have the devices share very little data. What might help is to systematically reason about things the chips must be doing, and things they can't be doing. That will clearly outline the limits of theories.

They can be doing DES, where a chip can generate one of 32 DES keystreams (16 for lock and 16 for key) and verify the other one.

.

kevtris wrote:

This is the length distribution graph that Q made:

http://tripoint.org/kevtris/mappers/inc ... bution.jpg

http://tripoint.org/kevtris/mappers/inc ... bution.jpg

Fuck me?

(You forgot to add nesdev.com and nesdev.com to the whitelist.)

.

I tried to get my parallel port to log the CIC in action but had no luck. Not sure what the problem is. I'm sure I'll get it right eventually. Or maybe I'll just do what Kevin suggested and break out a FPGA.

While messing with the CIC logger I was trying to make, I got an idea on another way to beat this system. When no cart is in the NES, the system isn't in reset the whole time. If we could disrupt the clock signal going to the Lock while the system is on, the lock won't be able to function and the NES will stay on. Ofcourse for this to work it would require messing the clock signal up enough to halt the MPU in the lock. But at the same time it can't damage the oscillator. Would this be possible?

I got it to work on the bread board pretty easily by just removing the clock signal wire. Anybody know a good way to stop the clock without damage? I have no problem with testing this on one of my nintendos, worst case scenario I have to remove the CIC altogether.

While messing with the CIC logger I was trying to make, I got an idea on another way to beat this system. When no cart is in the NES, the system isn't in reset the whole time. If we could disrupt the clock signal going to the Lock while the system is on, the lock won't be able to function and the NES will stay on. Ofcourse for this to work it would require messing the clock signal up enough to halt the MPU in the lock. But at the same time it can't damage the oscillator. Would this be possible?

I got it to work on the bread board pretty easily by just removing the clock signal wire. Anybody know a good way to stop the clock without damage? I have no problem with testing this on one of my nintendos, worst case scenario I have to remove the CIC altogether.

You could always open a Game Pak, cut pin 4 on the CIC, and then wire up two Game Paks' CICs in a lock/key configuration.

tepples wrote:

You could always open a Game Pak, cut pin 4 on the CIC, and then wire up two Game Paks' CICs in a lock/key configuration.

I think you'll need to wire the pin to VCC, not just cut it. Cut it on the NES PCB has the effect to tie it to GND, for some reason. But it won't be the same between 2 game paqs. And yeah, that is a great idea, because there is no NES invoved, and this avoid lots of problems, such as risk to damage the console or mecanical issues.

Bregalad wrote:

tepples wrote:

You could always open a Game Pak, cut pin 4 on the CIC, and then wire up two Game Paks' CICs in a lock/key configuration.

I think you'll need to wire the pin to VCC, not just cut it.

I intended that to be implicit in "wire up two CICs in lock/key". You cut pin 4 so that you can turn a key into a lock. Or you can just desolder the two CICs completely and put them in a breadboard.

Quote:

And yeah, that is a great idea

Thanks.

Has anybody tried to photograph the insides of the Rabbit chip from Tengen games yet?

tepples wrote:

I intended that to be implicit in "wire up two CICs in lock/key". You cut pin 4 so that you can turn a key into a lock. Or you can just desolder the two CICs completely and put them in a breadboard.

Disolver a 14 pin DIL chip on a PCB with solver on both sides without doing serious damage to the chip is nearly impossible.

Assuming "disolver" is supposed to be "desolder", you're wrong - you can most certainly desolder a 14-pin DIL chip from a double-sided board without damaging it IF you have the proper tools. With a decent desoldering iron, it's quite easy, though it's still doable with a spring-loaded solder-sucker (but slow) or even copper braid solder wick (though it'd take a LONG time).

Zack S wrote:

I tried to get my parallel port to log the CIC in action but had no luck. Not sure what the problem is. I'm sure I'll get it right eventually. Or maybe I'll just do what Kevin suggested and break out a FPGA.

The problem is, you must reset the CIC for it to start working. If you don't, the CIC will get very hot! I dunno why this is, but it does. When working normally, the CIC does not get warm.

Quote:

While messing with the CIC logger I was trying to make, I got an idea on another way to beat this system. When no cart is in the NES, the system isn't in reset the whole time. If we could disrupt the clock signal going to the Lock while the system is on, the lock won't be able to function and the NES will stay on. Ofcourse for this to work it would require messing the clock signal up enough to halt the MPU in the lock. But at the same time it can't damage the oscillator. Would this be possible?

That won't work. They use two separate inverters on the 74HCU04 to individually buffer CLK to each CIC.

Quote:

I got it to work on the bread board pretty easily by just removing the clock signal wire. Anybody know a good way to stop the clock without damage? I have no problem with testing this on one of my nintendos, worst case scenario I have to remove the CIC altogether.

Just remove two CICs from two cartridges and use those... Though I am unclear if you can use the 6113 CICs back to back.

Speaking of this, I am kinda confused about why nintendo did this. The console *always* has a 3193 CIC in it (US console), while the carts have a 3193 (older) or 6113 (newer). I was wondering if the 6113 was a "key only" cost-reduced version or something... Even the very last versions of the front loader have the 3193 in it... So there must be some reason the 6113 is not usable as a lock.

kevtris wrote:

The problem is, you must reset the CIC for it to start working. If you don't, the CIC will get very hot! I dunno why this is, but it does. When working normally, the CIC does not get warm.

I had a Reset signal going to the Lock and a Clock signal going to both CIC's. It's probably just something wrong with my code or I misswired something.

kevtris wrote:

That won't work. They use two separate inverters on the 74HCU04 to individually buffer CLK to each CIC.

Guess it's back to trying to RE it.

kevtris wrote:

Just remove two CICs from two cartridges and use those... Though I am unclear if you can use the 6113 CICs back to back.

That's excactlt what I did. Both of the CIC's are 6113's that I took out of game carts. They work fine back to back, at least they seem to. Without the key connected it produce the reset squarewave for the NES. With the key connected it kept the NES out of reset.

Bredalad wrote:

Disolver a 14 pin DIL chip on a PCB with solver on both sides without doing serious damage to the chip is nearly impossible.

I used a 15$ desoldering iron to pull two CIC's off of PCB's, it took about a minute each. They worked fine in the breadboard so it didn't damage them. I usually do every 3rd pin or so, as opposed to just going down the line. That way each area of the chip has time to cool.

has anyone logged what the lock and key do when they are not connected to each other? also... has anyone logged the response from the key when given only part of the sequence from the lock and vice versa?

The legal docs from the Nintendo vs Tengen case mentioned that Nintendo modified the lockout code in 1987 ("deleted some instructions"), maybe that's when they changed the part #s for the chip?

WhoaMan wrote:

has anyone logged what the lock and key do when they are not connected to each other? also... has anyone logged the response from the key when given only part of the sequence from the lock and vice versa?

I haven't yet but plan to as soon as I get my data logger working. I got an oscilliscope toady so that should help me figure out whats not working.

Zack S wrote:

I got an oscilliscope toady so that should help me figure out whats not working.

Oscilloscope toadies from Yoshi's Island 2: Reverse Engineering

Quick update on my Parallel port data logger project. This will simply not work. I hooked up the O-scope and found that the parallel port can't go fast enough for the CIC. I'm guessing that the part of the chip depends on dynamic RAM, that isn't getting refreshed fast enough with the slow clock cycle I'm giving it.

I'm still learning to work with FPGA's so it could be some time before I make a data logger for it.

I'm still learning to work with FPGA's so it could be some time before I make a data logger for it.

I really doubt it has dynamic RAM in it. It could be some other asynchronous element in it like the older time-delay digital logic design that uses resistors and capacitor (RC) elements instead of clocked logic.

Moved from NESdev to NES Hardware / CopyNES, as the CIC's functionality isn't really related to NES programming.

kevtris wrote:

One interesting thing is that there are no runs shorter than 87 clocks I believe it was. In all my testing, one "clock" was made up of 4 clock cycles to the lockout chips.

I was thinking about this, comparing it to the patent document, and it doesn't make sense to me. According to the document there is the initial exchange, to seed the first random number (select the sequence) and then there is a transaction once per 4 clocks. I'll explain:

The 4Mhz clock is divided by 4 and split into four separate clocks in each of the four possible phases - and they are called phi1 through phi4. The patent suggests that on phi1 data is read in from the IO port. The next two cycles (phi2 and phi3) are used for "predetermined arithmetic operations". Then, on phi4 the data is output to IO. This sequence is repeated indefinately.

If I'm understanding this correctly, the data that is read in on phi1 as well as the data output in phi4 can't be anything other than 1 bit in size. It seems unlikely that the distribution would allow for runs of 87 cycles and longer without a single result of "1". Am I missing something here? Are the patent documents not quite accurate? I'm very suspicious of the explaination of the synchronization explained in there, it doesn't match the logic analyzer logs posted.

edit: I just realized that the "1" in the logs from Kev's tester are 3 clocks long.... which is a big clue. It indicates it's operating on the divided clocks and not on the original. I'm thinking there's some kind of "pipeline" going on here.

bunnyboy wrote:

I put all my text files in a new directory at www.nesmuseum.com/10nes

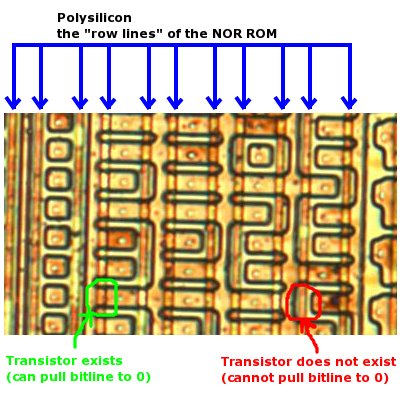

nescicrom.txt - nes lockout rom dump, directly from rom array. Bits and bytes are interleaved, figuring out how it is actually arranged is part of the problem.

nescicrom.txt - nes lockout rom dump, directly from rom array. Bits and bytes are interleaved, figuring out how it is actually arranged is part of the problem.

I had downloaded the photos taken by Nevitski with the microscope of the NES CIC, and started to decode them myself. I didn't make it all the way through - only 144 bytes in. However, comparing what I have against what you posted I found a discrepancy. Below I will paste the content of your nescicrom.txt, but will put an "X" in the location where I came up with a different value than you did. You have a "1" in that spot, and I read it as "0". In the 1152 bits that I decoded, we only differ by one bit... which means we're either reading it correctly, or at least consistantly incorrect.

1111100010111010001110100111111001111110010111000011101011101110

0110011110111111001101011111X11101100101011011010011010111011111

Unfortunately one bit difference out of over 1000 doesn't help us decode it at all. But it points out having several people decode it independently might help us reduce errors in it. If I get time, I'll try to keep decoding more.

Contrary to what a lot of people think, Motorola DID design a 4-bit cpu:

The MC141000.

This MIGHT be the processor used in the Tengen CIC clone.

I managed to dig up the datasheets for it in one of the lab rooms around campus, where they had copies of many of the old Motorola databooks.

As far as I'm aware, the datasheets are unavailable on the internet.

The last page has the instruction set on it.

Scans: (note that these require some image rotation)

http://www.netaxs.com/~gevaryah/MC141xxx001.png

http://www.netaxs.com/~gevaryah/MC141xxx002.png

http://www.netaxs.com/~gevaryah/MC141xxx003.png

http://www.netaxs.com/~gevaryah/MC141xxx004.png

http://www.netaxs.com/~gevaryah/MC141xxx005.png

Lord Nightmare AKA Jonathan Gevaryahu

lord(underscore)nightmare (@t) users (d0t) sf (d0t) net

The MC141000.

This MIGHT be the processor used in the Tengen CIC clone.

I managed to dig up the datasheets for it in one of the lab rooms around campus, where they had copies of many of the old Motorola databooks.

As far as I'm aware, the datasheets are unavailable on the internet.

The last page has the instruction set on it.

Scans: (note that these require some image rotation)

http://www.netaxs.com/~gevaryah/MC141xxx001.png

http://www.netaxs.com/~gevaryah/MC141xxx002.png

http://www.netaxs.com/~gevaryah/MC141xxx003.png

http://www.netaxs.com/~gevaryah/MC141xxx004.png

http://www.netaxs.com/~gevaryah/MC141xxx005.png

Lord Nightmare AKA Jonathan Gevaryahu

lord(underscore)nightmare (@t) users (d0t) sf (d0t) net

Lord Nightmare wrote:

Contrary to what a lot of people think, Motorola DID design a 4-bit cpu:

The MC141000.

This MIGHT be the processor used in the Tengen CIC clone.

The MC141000.

This MIGHT be the processor used in the Tengen CIC clone.

How surprising, I've never heard of it. The only 4-bit CPU I've ever heard about it the Intel 4040.

Might it be the processor used in the real CIC microcontroller ?

Kevin since you already have a data logger on hand. Maybe you could program it so instead of just recording the whole stream of data, It could record the first few transitions and then just keep looking for it to repeat. Then we might be able to find out how long it takes to repeat with out having to fill up a harddrive. That could give us a pretty good idea of how secure it really is.

Zack S wrote:

Kevin since you already have a data logger on hand. Maybe you could program it so instead of just recording the whole stream of data, It could record the first few transitions and then just keep looking for it to repeat. Then we might be able to find out how long it takes to repeat with out having to fill up a harddrive. That could give us a pretty good idea of how secure it really is.

It's not possible to "look for it to repeat" without logging the entire data stream. The last stream kevtris logged was nearly 7 minutes worth of real-time data - which took many hours to dump and occupied over 400 megabytes of space (since it stored only 1 cycle per byte, using a few of the upper bits for sequence numbers to make sure the serial datastream never skipped any bytes) - and it didn't repeat.

Quietust wrote:

It's not possible to "look for it to repeat" without logging the entire data stream.

I don't understand why you come to this conclusion. You record a very short sample of the stream when it begins, then simply read the stream following and if it doesn't match the recorded beginning discard the data and retrieve the next section. Since the signal is so sparse it should allow plenty of time for the comparison. Once you find a spot that matches you could verify that it is repeating by restarting and logging every Nth number output that way you don't need huge amounts of data but still get a good comparison to verify it is indeed repeating.

On another topic. I have read the cherryrom forum like 3 times now and gone though the patent twice. How feasable would it be to try and read some of the CPU core circuitry. I have a pretty good knowledge of this sort of thing and could probably produce most of the instruction set if I had a good schematic of the CPU Core. I would be willing to get a microscope and other needed items if It would allow me a better look at the internal circuitry.

Has anyone already taken usable pictures of this already?

Thanks again for all the help.

Considering how random the data is, you would have to read a very long segment in order to insure that the data really DID repeat - otherwise you could easily be thrown off. Consider this example:

123456789079084325897324059734850972348509724509872435809723450987908790837980790825902835

123456789013459632485732459534759018709463298174893274980632174612409382754326574359083745

123456789078346159045967094586767096867860983568920359034868798089748679827349580734985737

Using your logic, you would have detected two repeats based on the string "1234567890", but the string clearly does not repeat at all in the sample space provided.

123456789079084325897324059734850972348509724509872435809723450987908790837980790825902835

123456789013459632485732459534759018709463298174893274980632174612409382754326574359083745

123456789078346159045967094586767096867860983568920359034868798089748679827349580734985737

Using your logic, you would have detected two repeats based on the string "1234567890", but the string clearly does not repeat at all in the sample space provided.

Why is everyone expecting the stream to repeat? Maybe it just wont. I don't know much about this, and I should probably be quiet, but I think that decoding the program is still the best bet.

It really amazes me that this thing wasn't figured out yet... This chip is so old and there are so many amazing people in nesdev! it is a mistery why this chip wasn't figured out yet.

It really amazes me that this thing wasn't figured out yet... This chip is so old and there are so many amazing people in nesdev! it is a mistery why this chip wasn't figured out yet.

Quote:

It really amazes me that this thing wasn't figured out yet... This chip is so old and there are so many amazing people in nesdev! it is a mistery why this chip wasn't figured out yet.

I agree, plus all SNES dev people have the same sheme.

All random number generation repeats, even if the string is very very very long. However, since the binary has been decoded, I think, some people that are able to do it should try to see what it looks with all processors back then.

Quote:

Why is everyone expecting the stream to repeat? Maybe it just wont. I don't know much about this, and I should probably be quiet, but I think that decoding the program is still the best bet.

The two chips both generate a sequence and verify that the other is generating the same. Unless they somehow connect to a single quantum random number source or something (only joking here), the sequence must be generated using a finite deterministic process, thus it must repeat. Repeatability is the same principle that lets emulators record movies by only keeping the joypad input.

Bregalad wrote:

However, since the binary has been decoded, I think, some people that are able to do it should try to see what it looks with all processors back then.

I have been trying to work with the ROM dump, but everyone seems unsure of how it is interleaved, where the data bus connects, how the address is decoded etc. A lot of the HEX code generated, has been either 0 or F wich doesn't seem right to me. Unless they're no op instruction inserted in the code for timing purposes.

Not to mention some other unknowns like how the key/lock pin is connected. It could be a port that is read or it could simply be hooked up to the ROM's highest address bit, effectively dividing the ROM into two seperate chunks. One for each function.

If we knew for sure that we are looking at the instructions in sequential order, I'm sure we could attach some meaningfull assembly commands to the code using the 10NES flow chart.

Well, I really cannot say anything here, because I really have no experience with reverse-engineering.

May I ask a stupid question ? How was people able to reverse-engineer the NES (or other machines) to figure out how the PPU, APU cartridge banking, etc... works ? Okay, it is said that the console have a 6502 and you can read the text inside the cartridge to know wich chips are the maskrom, but you don't know their pinout, and you don't know wich bus adress is what, etc...

It seems just impossible to figure out. Well, the very first older NROM game has regular pinout, so it would be possible to dump them, and to look at the 6502 code to figure out how the registers are written to. From there, you can replace the ROM, and try about anything. So you can figure pretty much how the adress buses works, and so can work with more advanced cartridge. However, with absolutely no known about how works pattern tables, name tables, palettes, it would be long long hours of work to try to change any value from the original game to see what's happening.

That's for NES, but for SNES, the hardware is much more complicated. And for the GBA, due to the size of the cartridges, the fact that everything is surface-mounted, etc...... well, I stop saying stupid things. Those HAD been reverse-engineered.

May I ask a stupid question ? How was people able to reverse-engineer the NES (or other machines) to figure out how the PPU, APU cartridge banking, etc... works ? Okay, it is said that the console have a 6502 and you can read the text inside the cartridge to know wich chips are the maskrom, but you don't know their pinout, and you don't know wich bus adress is what, etc...

It seems just impossible to figure out. Well, the very first older NROM game has regular pinout, so it would be possible to dump them, and to look at the 6502 code to figure out how the registers are written to. From there, you can replace the ROM, and try about anything. So you can figure pretty much how the adress buses works, and so can work with more advanced cartridge. However, with absolutely no known about how works pattern tables, name tables, palettes, it would be long long hours of work to try to change any value from the original game to see what's happening.

That's for NES, but for SNES, the hardware is much more complicated. And for the GBA, due to the size of the cartridges, the fact that everything is surface-mounted, etc...... well, I stop saying stupid things. Those HAD been reverse-engineered.

The simple answer to why this hasn't been reverse engineered is that it's really difficult. It's much more difficult than an MMC chip for example, because it's external interface doesn't give away much of what it does. If you want to get an idea of how difficult it is, read this phd thesis on the topic:

Intro

http://www.cl.cam.ac.uk/~sps32/mcu_lock.html

Full paper

http://www.cl.cam.ac.uk/TechReports/UCAM-CL-TR-630.pdf

There are several interesting and pretty doable approaches mentioned there, but the equipment and cost for most of them is pretty steep. Our best bet is to get a full optical picture of the decapped chip, learn some VLSI, and start RE'ing the thing. The full optical scan is very difficult unless you have a microscope that does this automatically, because at the 500x magnification you need, you need to take a LOT of photos and stitch them together.

Although, if we can decode enough of the area around the ROM to learn how the bits are interleaved, that's a pretty good start.

Intro

http://www.cl.cam.ac.uk/~sps32/mcu_lock.html

Full paper

http://www.cl.cam.ac.uk/TechReports/UCAM-CL-TR-630.pdf

There are several interesting and pretty doable approaches mentioned there, but the equipment and cost for most of them is pretty steep. Our best bet is to get a full optical picture of the decapped chip, learn some VLSI, and start RE'ing the thing. The full optical scan is very difficult unless you have a microscope that does this automatically, because at the 500x magnification you need, you need to take a LOT of photos and stitch them together.

Although, if we can decode enough of the area around the ROM to learn how the bits are interleaved, that's a pretty good start.

Bregalad wrote:

Well, the very first older NROM game has regular pinout

I once read a story of how an unlicensed shop (Color Dreams? Tengen?) cracked the NES. At that point, they had dumped the PRG ROM and CHR ROM of Mario Bros. PRG was found to contain byte sequences common in 6502 bytecode, and CHR was decoded using a simple tile editor similar to those used to develop for other consoles, 8-bit microcomputers, and arcade systems. With the CHR, they could discover the character encoding that the PRG uses for text.

Bregalad wrote:

However, with absolutely no known about how works pattern tables, name tables, palettes, it would be long long hours of work to try to change any value from the original game to see what's happening.

A bit/bpl loop means "wait for this bit to become set", so $2002 must be a status register of sorts that periodically sets bit 7 to 1. This is enough to get the game into an infinite jmp loop when running in a generic 6502 simulator. An infinite loop likely means that the program is waiting for an interrupt to do something, so they explored the vectors and saw what happened when they triggered NMI.

At the same time, they searched for text in the ROM and then pointers to that text. A write-to-screen subroutine would use such a pointer to text. In the generic 6502 sim, place a breakpoint on reads from addresses inside text strings, and the PC is likely to be within a write-to-screen loop. So $2007 must be an output port to which things are written. Et cetera.

But if you don't have access to the PRG ROM bytes in order, and/or the processor's architecture is unfamiliar, you can't do all this as easily. Heck, unlike with carts soldered onto a PCB, you don't even have any traces to plug in a logic analyzer.

You mean reverse engineering is usually based by seeing how the silicium connexions are made inside the chip ? That's real crazy. It would take an incredible number of days to fully understand what those little connexions mean. Well, I think this is usefull anyway, even if it is a lot of hard-work.

I just got a pile of World Class Service tech manuals, there is sooo much interesting stuff in them. There is almost no information about the CIC but some of the cart pinouts have a more detailed pinout of the CIC. No idea how this helps anything...

1 OUT (to nes)

2 IN (from nes)

3 R02 (unconnected)

4 SEL (gnd, lock/key)

5 CL2 (unconnected)

6 CLK (from nes)

7 RST (from nes)

8 GND

9 R10 (unconnected)

10 R11 (unconnected)

11 R12 (unconnected)

12 R13 (unconnected)

13 R20 (unconnected)

14 R21 (unconnected)

15 R22 (unconnected)

16 Vcc

Some of the other cart schematics show R02, R12, R13, R20, R21, R22 connected to ground, but R10, R11, CL2 still unconnected.

1 OUT (to nes)

2 IN (from nes)

3 R02 (unconnected)

4 SEL (gnd, lock/key)

5 CL2 (unconnected)

6 CLK (from nes)

7 RST (from nes)

8 GND

9 R10 (unconnected)

10 R11 (unconnected)

11 R12 (unconnected)

12 R13 (unconnected)

13 R20 (unconnected)

14 R21 (unconnected)

15 R22 (unconnected)

16 Vcc

Some of the other cart schematics show R02, R12, R13, R20, R21, R22 connected to ground, but R10, R11, CL2 still unconnected.

we should try dumping the 16 streams that the lock spits out from when it is first powered until it toggles the 1hz reset line... then compare these to the 16 streams spit out by both the Lock and Key and try to determine where the break in communication affects the lock. has anyone logged the streams in an unconnected CIC?

So how's the electron microscope effort coming along?

-Rob

-Rob

Speculation based on loopy's data: the nes CIC patent is correct: the clock is divided by four before it is used by the chip internals.

according to the patent:

phase 1(0) = cpu reads input

phase 2(1) = arithmetic operation 1

phase 3(2) = arithmetic operation 2 or continuation of 1

phase 4(3) = cpu sets output (external lines come active on the ?falling edge of this clock? according to column 5, line 35-40 in the patent)

my guess for the first cycle of the cic based on the patent is it reads pin 5 and does a conditional jump (or less likely, a variable set) depending on whether it is a lock or key. I can't tell much else.

Also the preamble transmitted by the master? cic seems to be for both key specification (i.e. master provides TWO 4-bit numbers to the slave, one is 'my key' and one is 'your key', hence how both know which key the other is sending to compare to) and to phase-desynchronize the slave cic to it somehow, because if both chips were running at exactly the same phase, the patterns of ..0001332000.. we see wouldn't show up, they'd be ..000333000..

Lord Nightmare AKA Jonathan Gevaryahu

lord_nightmare (@t) users (d0t) sf (d0t) net

according to the patent:

phase 1(0) = cpu reads input

phase 2(1) = arithmetic operation 1

phase 3(2) = arithmetic operation 2 or continuation of 1

phase 4(3) = cpu sets output (external lines come active on the ?falling edge of this clock? according to column 5, line 35-40 in the patent)

my guess for the first cycle of the cic based on the patent is it reads pin 5 and does a conditional jump (or less likely, a variable set) depending on whether it is a lock or key. I can't tell much else.

Also the preamble transmitted by the master? cic seems to be for both key specification (i.e. master provides TWO 4-bit numbers to the slave, one is 'my key' and one is 'your key', hence how both know which key the other is sending to compare to) and to phase-desynchronize the slave cic to it somehow, because if both chips were running at exactly the same phase, the patterns of ..0001332000.. we see wouldn't show up, they'd be ..000333000..

Lord Nightmare AKA Jonathan Gevaryahu

lord_nightmare (@t) users (d0t) sf (d0t) net

If someone wanted to post a binary or text version of the CIC output and provide hours of data I would want to number crunch it. I think saving the timestamp and states when the state does change would be a good format. I don't mind trying to brute force this thing but if we're going to do it that way I will need lots of data to analyze.

I do appreciate the data already posted but I'll need more to try to brute force this thing. I don't have the neccessary equipment to record the pulses or I would be working on this on my own.

I do appreciate the data already posted but I'll need more to try to brute force this thing. I don't have the neccessary equipment to record the pulses or I would be working on this on my own.

I think there's only one 4-bit key. It may be that the key generates pairs of pseudo-random bits at a time, with the lock sending one of the two bits and the key sending the other.

I doubt that the misalignment between the two CICs (the "013320") has any significance. It's probably just a side-effect of how the chips get synchronized (one happens to be one step off). My guess is the CIC follows a procedure like "Write output; Read input; Wait a cycle; Clear output"), where the setting and clearing of the output data occur three steps apart and the reading occurs in the middle. As long as the middle read occurs while the other chip still has valid output, the system will work even if the chips are slightly out of alignment (which is obviously the case).

I doubt that the misalignment between the two CICs (the "013320") has any significance. It's probably just a side-effect of how the chips get synchronized (one happens to be one step off). My guess is the CIC follows a procedure like "Write output; Read input; Wait a cycle; Clear output"), where the setting and clearing of the output data occur three steps apart and the reading occurs in the middle. As long as the middle read occurs while the other chip still has valid output, the system will work even if the chips are slightly out of alignment (which is obviously the case).

This topic has interested me for a couple of year.

It would be very interesting to know how the CIC works.

A very good start would probably be to dig out all information on

4 bit micros around that time and then write dissassemblers for them.

Assuming the bitordering is done correctly it would probably

show right away, as long as it's not a custom type cpu.

If the instructions makes any sense it's probably a candidate cpu.

It could be as the maincpu of the gameboy, a standard cpu (in this case z80) but modified to a certain degree.

I tried to look up some datasheets of old 4 bit micros, but it's really a jungle.

That im limited to a 56k modem at the moment doesn't really help either -_-

One way might be to try to find docs of who were nintendo partners at

the time, possibly numbers. As CICs were included in about every game,

it would probably showup somewhere.

It would be very interesting to know how the CIC works.

A very good start would probably be to dig out all information on

4 bit micros around that time and then write dissassemblers for them.

Assuming the bitordering is done correctly it would probably

show right away, as long as it's not a custom type cpu.

If the instructions makes any sense it's probably a candidate cpu.

It could be as the maincpu of the gameboy, a standard cpu (in this case z80) but modified to a certain degree.

I tried to look up some datasheets of old 4 bit micros, but it's really a jungle.

That im limited to a 56k modem at the moment doesn't really help either -_-

One way might be to try to find docs of who were nintendo partners at

the time, possibly numbers. As CICs were included in about every game,

it would probably showup somewhere.

Hello,

Sorry for the long pause. Cherryroms is down, so I guess I'll continue this here. (Grrr... I'd like to be able to see my old posts/thoughts/work)

http://www.neviksti.com/CIC/tengen/

as the name suggests, this is the tengen CIC. I believe this is currently our only real hope of figuring out the program. The first thing is to identify the core used here (it is indeed something from Motorola, and appears to be 4-bit according to the SRAM organization). So have at it!

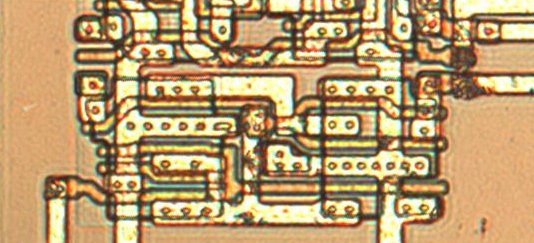

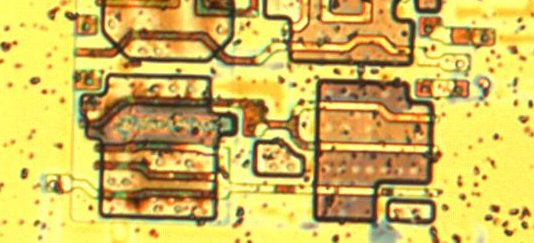

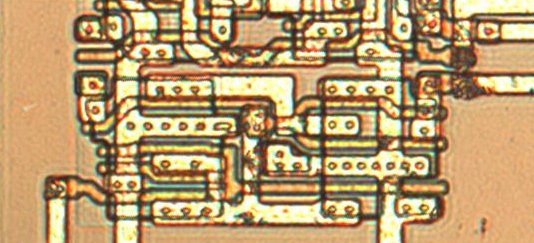

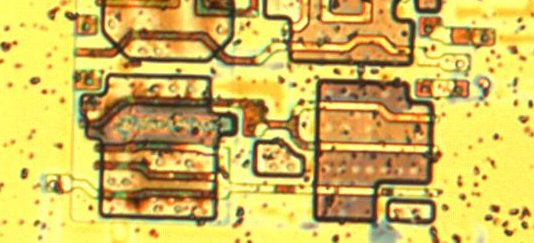

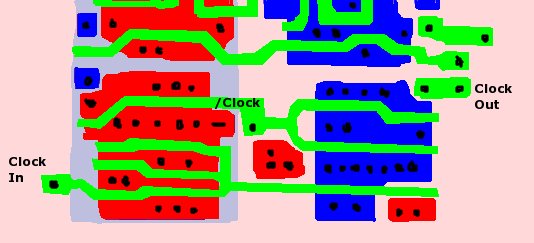

I have access to a much better camera now (for those that remember what the other CIC pictures looked like). I love the old chips, it is so easy to see everything! These pictures were taken with only a 100x lense. The next one is 500x, and I wasn't willing to take 25 times as many pictures as this alone took me two hours, so this is it for resolution. You can make out almost everything, so I think it will be okay for those that wanted to "trace" the circuit.

Reminder, there are three layers here: (top to bottom) metal, poly-silicon, bulk/silicon surface (you can sometimes make out the edges of the different doping regions).

I'm tired and think I'm done for the night. Can someone please combine these into a nice "one large picture", and maybe a shunken/overview version of that as well? It would be quite helpful.

I took the pictures snaking my way down the chip (ie every picture is adjacent to the last one), like this:

If you put the pictures together, you can upload it to a ftp space I setup here for everyone:

ftp.neviksti.com

user: CICpub

pass: pub987A

I'd also like to get all the CIC information people have into one place, so please ... if you have anything you think may be useful, please upload it for everyone to be able to read. Now that I have a bit more time, hopefully we can work together and figure out the mystery of this chip.

-neviksti

Sorry for the long pause. Cherryroms is down, so I guess I'll continue this here. (Grrr... I'd like to be able to see my old posts/thoughts/work)

http://www.neviksti.com/CIC/tengen/

as the name suggests, this is the tengen CIC. I believe this is currently our only real hope of figuring out the program. The first thing is to identify the core used here (it is indeed something from Motorola, and appears to be 4-bit according to the SRAM organization). So have at it!

I have access to a much better camera now (for those that remember what the other CIC pictures looked like). I love the old chips, it is so easy to see everything! These pictures were taken with only a 100x lense. The next one is 500x, and I wasn't willing to take 25 times as many pictures as this alone took me two hours, so this is it for resolution. You can make out almost everything, so I think it will be okay for those that wanted to "trace" the circuit.

Reminder, there are three layers here: (top to bottom) metal, poly-silicon, bulk/silicon surface (you can sometimes make out the edges of the different doping regions).

I'm tired and think I'm done for the night. Can someone please combine these into a nice "one large picture", and maybe a shunken/overview version of that as well? It would be quite helpful.

I took the pictures snaking my way down the chip (ie every picture is adjacent to the last one), like this:

Code:

--------+

|

+-------+

|

+-------+

|

+-------+

|

... etc

|

+-------+

|

+-------+

|

+-------+

|

... etc

If you put the pictures together, you can upload it to a ftp space I setup here for everyone:

ftp.neviksti.com

user: CICpub

pass: pub987A

I'd also like to get all the CIC information people have into one place, so please ... if you have anything you think may be useful, please upload it for everyone to be able to read. Now that I have a bit more time, hopefully we can work together and figure out the mystery of this chip.

-neviksti

Oh, I almost forgot...

I also depackaged a 6113A and 6113B1 (from US cartridges). I didn't take time to look at them under the microscope yet, but the B1 is smaller than the A. So it is probably just the same exact circuit and code, just taking advantage of newer fabrication technology.

And one last thing, I can see details much better than the camera made out, so I will hold off on trying to read the ROM in case people need to see a small portion better (because I have to etch away all the upper layers to get at the ROM ... in other words, if you have questions, ask them now as there is no looking back). I won't have time to try reading the ROM for awhile anyway, and if people want me to hold off even longer, of course that is fine as well.

I also depackaged a 6113A and 6113B1 (from US cartridges). I didn't take time to look at them under the microscope yet, but the B1 is smaller than the A. So it is probably just the same exact circuit and code, just taking advantage of newer fabrication technology.

And one last thing, I can see details much better than the camera made out, so I will hold off on trying to read the ROM in case people need to see a small portion better (because I have to etch away all the upper layers to get at the ROM ... in other words, if you have questions, ask them now as there is no looking back). I won't have time to try reading the ROM for awhile anyway, and if people want me to hold off even longer, of course that is fine as well.

Thanks. It's like christmas. But with a harder to open package.

Just shooing from the hip here (like I always do):

Is it completely out of the question to attempt to emulate the chip's actual function based entirely on the physical model of the chip? I mean, if all the transistor junctions are visible, then it's technically as good as a *really* hard to read schematic, right?

Of course the hard part would be automating the translation of that image data, as I'd imagine that doing it by hand would be far to error-prone. It would take some juggling of the contrast of each layer to bring out the right features, and then applying some image analysis.

I wouldn't expect to get a 100% perfect emulation out of such a thing. Instead, maybe something that can at least behave like a state machine, so the inner-workings of this thing can become a little more scutable. I'd suspect that things like on-chip inductors, capacitors, transistor switch timings (and god only knows what else - I'm no EE) would keep a few things out of reach, but the rest is doable IMO.

Is it completely out of the question to attempt to emulate the chip's actual function based entirely on the physical model of the chip? I mean, if all the transistor junctions are visible, then it's technically as good as a *really* hard to read schematic, right?

Of course the hard part would be automating the translation of that image data, as I'd imagine that doing it by hand would be far to error-prone. It would take some juggling of the contrast of each layer to bring out the right features, and then applying some image analysis.

I wouldn't expect to get a 100% perfect emulation out of such a thing. Instead, maybe something that can at least behave like a state machine, so the inner-workings of this thing can become a little more scutable. I'd suspect that things like on-chip inductors, capacitors, transistor switch timings (and god only knows what else - I'm no EE) would keep a few things out of reach, but the rest is doable IMO.

Glad to see you are back! The cherryroms forums are still in google cache, go grab them quick while you can. Let me know if you need me to send you more cic chips in case the first ones dont work.

The ASIC in picture 4 isnt promising, but it could just mean its standard micro inside custom package. I think the assumption has always been it was an 8 bit cpu because of the link to motorola. Mapping out every transistor will be crazy time consuming but could be the best option. I cant recognize transistor/gate structures, anyone have links to tutorials?

The ASIC in picture 4 isnt promising, but it could just mean its standard micro inside custom package. I think the assumption has always been it was an 8 bit cpu because of the link to motorola. Mapping out every transistor will be crazy time consuming but could be the best option. I cant recognize transistor/gate structures, anyone have links to tutorials?

WOW...awesome. Just how many layers are there?

-Rob

-Rob

pragma wrote:

Just shooing from the hip here (like I always do):

Is it completely out of the question to attempt to emulate the chip's actual function based entirely on the physical model of the chip? I mean, if all the transistor junctions are visible, then it's technically as good as a *really* hard to read schematic, right?

Is it completely out of the question to attempt to emulate the chip's actual function based entirely on the physical model of the chip? I mean, if all the transistor junctions are visible, then it's technically as good as a *really* hard to read schematic, right?

I had the same idea at one point. It seems possible to extract the netlist from the photo's, and create a model of the hardware using SPICE. Then, we could have a dynamic model to play with to help with the reverse engineering, as opposed to just the pictures.

I came to the conclusion that while feasible, it's a lot of work. I would consider it as a last resort, but I don't see it as impossible.

BTW, thanks a million Nevitski, your effort is much appreciated.

rbudrick wrote:

WOW...awesome. Just how many layers are there?

-Rob

I tried to answer this in my earlier post:

-Rob

Reminder, there are three layers here: (top to bottom) metal, poly-silicon, bulk/silicon surface (you can sometimes make out the edges of the different doping regions).

If you just overlooked it, that's fine, but if you are referring to something else and I'm misunderstanding, just let me know and I'll try to answer the question.

As for "complete specification" of the circuit ... nope, these pictures will not allow you to know all of that. Even though there are only three layers, the upper ones cover too much to completely see the lower ones. In particular, it is amazing that any of the diffusion layer can be seen.

What can these pictures be used for?

- You can see the organization of the memory (I still can't tell how many bits are in one instruction, can someone tell?).

- You can see how the address lines connect.

- You may be able to identify other components and how they connect / interact (to help determine the CPU core).

- An industrious individual may even be able to identify how the opcodes are "grouped" (ie usually all move commands have a vary similar opcode ... you could think of it as a couple bits are the "command" and other bits are the "arguements").

- Hopefully someone can figure out how the ROM bits are ordered before we try to read them out.

If you guys really want, I can try to remove just the upper oxide and metal interconnect layer, to get pictures of the middle layer. Then you probably could trace the entire circuit. I'm not confident I can remove the layers like that though.

As far as ASIC goes, I don't expect much to be custom besides the location and handling of the power and I/O pins. It would be wasteful of resources for them to try to create their own CPU core.

I seem to remember reading that the Tengen CIC clone was based on a standard Motorola 6800 series core.

tepples wrote:

I seem to remember reading that the Tengen CIC clone was based on a standard Motorola 6800 series core.

Where did you read this? I would like to check up on it if you have a lead.

Also, as usual, it is always worth it to pursue this from the human angle. Check out this article:

http://www.atarihq.com/tsr/special/el/el.html

Ed Logg: I walked into the lab and they were reverse engineering the chip, and I asked what they were doing and they said "Don't ask". (laughs) So I know the company was doing it, and I knew the people involved doing it.

It is a starting lead. All we need is for them to tell us what CPU core they used (I think this is a reasonable/possible question to get an answer to). Anyone willing to follow the trail?

Wow, killer interview. I'm surprised I hadn't seen that before.

Neviksti, if you are reasonably sure there's a good chance you can get to the other layer, I say go for it. It would probably be pretty useful.

Did anyone stitch these scans together?

Would it be easier to get the other side if you got another chip and went in through the bottom instead? Just a shot in the dark here since I've never pulled a chip like this apart before.

-Rob

Neviksti, if you are reasonably sure there's a good chance you can get to the other layer, I say go for it. It would probably be pretty useful.

Did anyone stitch these scans together?

Would it be easier to get the other side if you got another chip and went in through the bottom instead? Just a shot in the dark here since I've never pulled a chip like this apart before.

-Rob

Yeah, there's a stitched together pic on the server.

I wish I could tell more about it just from looking at the pics. I can't find any reasonably hires pics of many Motorla chips, from the looks of it I was lucky to find a pic at all of the 6800 here:

http://www.cpu-world.com/CPUs/6800/die/L_Motorola-MC6800L.jpg

http://www.cpu-world.com/CPUs/6800/die/L_AMI-S6800.jpg

I wish I could tell more about it just from looking at the pics. I can't find any reasonably hires pics of many Motorla chips, from the looks of it I was lucky to find a pic at all of the 6800 here:

http://www.cpu-world.com/CPUs/6800/die/L_Motorola-MC6800L.jpg

http://www.cpu-world.com/CPUs/6800/die/L_AMI-S6800.jpg

rbudrick wrote:

Neviksti, if you are reasonably sure there's a good chance you can get to the other layer, I say go for it. It would probably be pretty useful.

I thought about it and decided I'd like to make sure we're "done" with this top layer first, before continuing.

(I'm willing to take higher res photos of small regions, like how the SRAM is addressed, and how the ROM is addressed or something. However, due to the time required, I probably won't do that unless there's a specific thing I'm looking for... specific connection question I am trying to answer that can't be seen in the current pics.)