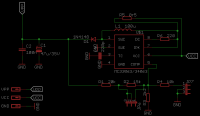

In order to learn some basic info about eprom programmer I want to make this : EPROMr

It seems that the source code of the software is not available, so I wrote my own :

But I haven't tested it yet.

Do I have to use any delay between clocks inside of the for loop?

By the way my code is only for 27C080 (1MB) EPROM.

It seems that the source code of the software is not available, so I wrote my own :

Code:

#include <stdio.h>

#include <dos.h>

void main ()

{

long int i;

outportb ( 0x37A, inportb(0x37A) & 254 ); /* Set reg0 [pin1] to low >> set reset to high */

outportb ( 0x37A, inportb(0x37A) | 1 ); /* Set reg0 [pin1] to high >> set reset to low */

FILE *fp;

fp=fopen ("read_eprom.bin", "wb"); /* Create a file to store data of eprom */

for ( i=1 ; i<=1048576 ; i=i+1 ) /* 1048576 dec = 100000 hex */

{

putc (inportb(0x378), fp); /* Read eprom data and save it to the file */

outportb ( 0x37A, inportb(0x37A) | 4 ); /* Set reg2 [pin16] to high >> set clock to high */

outportb ( 0x37A, inportb(0x37A) & 251 ); /* Set reg2 [pin16] to low >> set clock to low */

}

fclose(fp);

}

#include <dos.h>

void main ()

{

long int i;

outportb ( 0x37A, inportb(0x37A) & 254 ); /* Set reg0 [pin1] to low >> set reset to high */

outportb ( 0x37A, inportb(0x37A) | 1 ); /* Set reg0 [pin1] to high >> set reset to low */

FILE *fp;

fp=fopen ("read_eprom.bin", "wb"); /* Create a file to store data of eprom */

for ( i=1 ; i<=1048576 ; i=i+1 ) /* 1048576 dec = 100000 hex */

{

putc (inportb(0x378), fp); /* Read eprom data and save it to the file */

outportb ( 0x37A, inportb(0x37A) | 4 ); /* Set reg2 [pin16] to high >> set clock to high */

outportb ( 0x37A, inportb(0x37A) & 251 ); /* Set reg2 [pin16] to low >> set clock to low */

}

fclose(fp);

}

But I haven't tested it yet.

Do I have to use any delay between clocks inside of the for loop?

By the way my code is only for 27C080 (1MB) EPROM.

_4040208%5EC_sml.jpg)