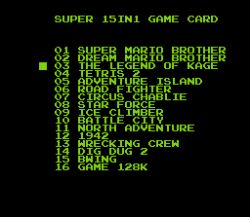

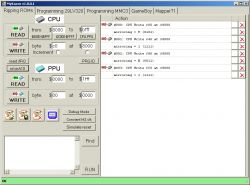

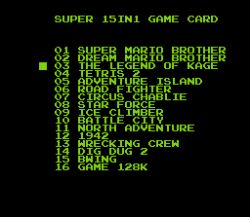

Funny NROM/UNROM multicart that also maps ROM at $6000 (in fact, the whole menu code is ran only from $6000-$7fff)

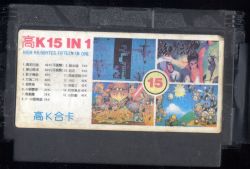

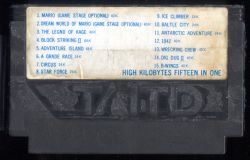

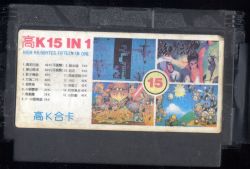

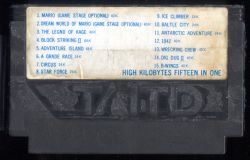

Whats the point of writing game sizes on the label? And look at the back of the shell

Whats the point of writing game sizes on the label? And look at the back of the shell

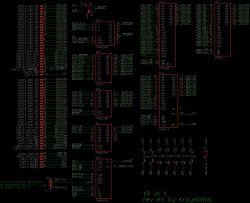

Code:

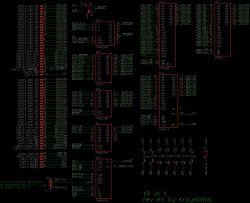

PRG:

ROM1 512 kB,

ROM2 128kB, unpopulated

CHR:

RAM 8 kB, can be write protected

Bus conflicts: no

REGISTERS (both cleared on powerup but NOT reset):

$8000-bfff:

fedcba9876543210 76543210

A~[10w.............] D~[ABCDE...]

| |||||

| |||++---- PRG outer bank

| |++------ PRG mode: 00=NROM 16k, 01=NROM 32k, 10/11=UNROM,

| |++------ PRG chip select: 00/01/10=PRG1, 11=PRG2

| |+------- CHR-ROM write protection: 0=enabled, 1=disabled

| ++------- mirroring: 00=V, 10=H, 01/11=1ScB(CIR_A10=VCC)

+--------------------------- write protection of both registers: 0=disabled, 1=enabled

$c000-ffff:

fedcba9876543210 76543210

A~[11..............] D~[.....FGH]

|||

+++- PRG inner bank (H ignored in NROM 32k)

$6000 mapped to second half of first 16kB from PRG1 (second 8kB bank)

BC | $6000 | $8000 | $c000

00 | PRG1=000001 | PRG1=DEFGH | PRG1=DEFGH

01 | PRG1=000001 | PRG1=DEFG0 | PRG1=DEFG1

10 | PRG1=000001 | PRG1=DEFGH | PRG1=DE111

11 | PRG1=000001 | PRG2=DEFGH | PRG2=DE111

PAL equations:

PRG2_nCE = (!CPU_RnW) | (!REG1_D5) | (!REG1_D6) | (CPU_nROMSEL);

PRG1_nCE = (REG1_D6 & REG1_D5 & !CPU_nROMSEL) | (!CPU_A14 & CPU_nROMSEL) | (!CPU_A13 & CPU_nROMSEL) | (!CPU_RnW);

PRG_A18 = (REG1_D4 & !CPU_nROMSEL);

PRG_A17 = (REG1_D3 & !CPU_nROMSEL);

PRG_A16 = (REG1_D6 & CPU_A14 & !CPU_nROMSEL) | (REG2_D2 & !CPU_nROMSEL);

PRG_A15 = (REG1_D6 & CPU_A14 & !CPU_nROMSEL) | (REG2_D1 & !CPU_nROMSEL);

PRG_A14 = (!REG1_D5 & REG2_D0 & !CPU_nROMSEL) |

(REG1_D5 & CPU_A14 & !CPU_nROMSEL) |

(REG1_D6 & REG2_D0 & !CPU_nROMSEL) |

(REG1_D6 & CPU_A14 & !CPU_nROMSEL);

ROM1 512 kB,

ROM2 128kB, unpopulated

CHR:

RAM 8 kB, can be write protected

Bus conflicts: no

REGISTERS (both cleared on powerup but NOT reset):

$8000-bfff:

fedcba9876543210 76543210

A~[10w.............] D~[ABCDE...]

| |||||

| |||++---- PRG outer bank

| |++------ PRG mode: 00=NROM 16k, 01=NROM 32k, 10/11=UNROM,

| |++------ PRG chip select: 00/01/10=PRG1, 11=PRG2

| |+------- CHR-ROM write protection: 0=enabled, 1=disabled

| ++------- mirroring: 00=V, 10=H, 01/11=1ScB(CIR_A10=VCC)

+--------------------------- write protection of both registers: 0=disabled, 1=enabled

$c000-ffff:

fedcba9876543210 76543210

A~[11..............] D~[.....FGH]

|||

+++- PRG inner bank (H ignored in NROM 32k)

$6000 mapped to second half of first 16kB from PRG1 (second 8kB bank)

BC | $6000 | $8000 | $c000

00 | PRG1=000001 | PRG1=DEFGH | PRG1=DEFGH

01 | PRG1=000001 | PRG1=DEFG0 | PRG1=DEFG1

10 | PRG1=000001 | PRG1=DEFGH | PRG1=DE111

11 | PRG1=000001 | PRG2=DEFGH | PRG2=DE111

PAL equations:

PRG2_nCE = (!CPU_RnW) | (!REG1_D5) | (!REG1_D6) | (CPU_nROMSEL);

PRG1_nCE = (REG1_D6 & REG1_D5 & !CPU_nROMSEL) | (!CPU_A14 & CPU_nROMSEL) | (!CPU_A13 & CPU_nROMSEL) | (!CPU_RnW);

PRG_A18 = (REG1_D4 & !CPU_nROMSEL);

PRG_A17 = (REG1_D3 & !CPU_nROMSEL);

PRG_A16 = (REG1_D6 & CPU_A14 & !CPU_nROMSEL) | (REG2_D2 & !CPU_nROMSEL);

PRG_A15 = (REG1_D6 & CPU_A14 & !CPU_nROMSEL) | (REG2_D1 & !CPU_nROMSEL);

PRG_A14 = (!REG1_D5 & REG2_D0 & !CPU_nROMSEL) |

(REG1_D5 & CPU_A14 & !CPU_nROMSEL) |

(REG1_D6 & REG2_D0 & !CPU_nROMSEL) |

(REG1_D6 & CPU_A14 & !CPU_nROMSEL);